## Chapter 8 Intra-Node Tuning

FUJITSU LIMITED April 2016

Copyright 2016 FUJITSU LIMITED

### Contents (1/2)

#### CPU Tuning

- What Is CPU Tuning (Intra-Node Tuning)?

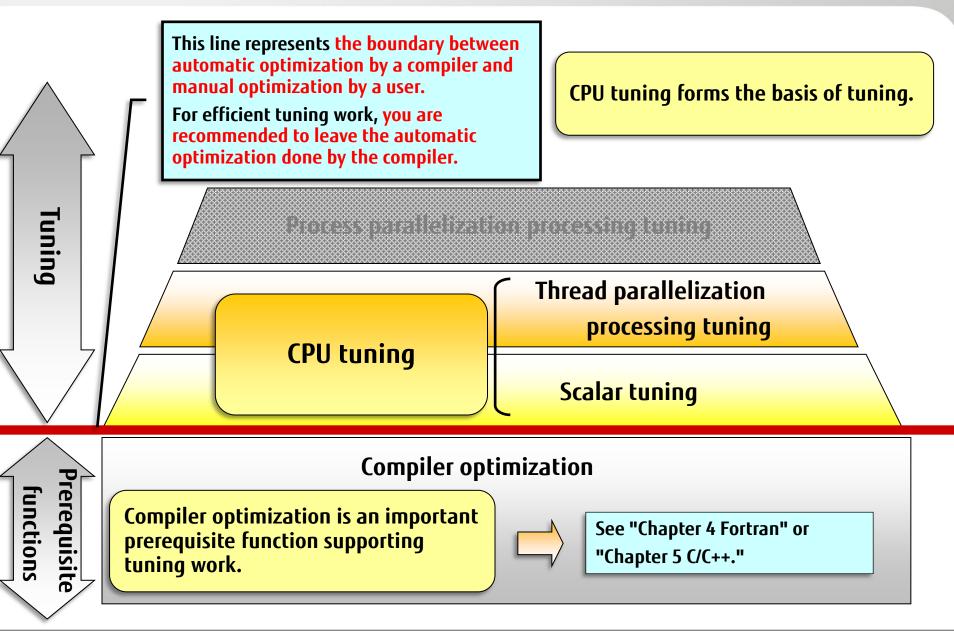

- Positioning of CPU Tuning

### How to Effectively Use PA Information and Tuning Flows

### Contents (2/2)

- Navigation from PA Information to Tuning Techniques

Tuning Map

- Tuning Technique List

- Scalar Tuning

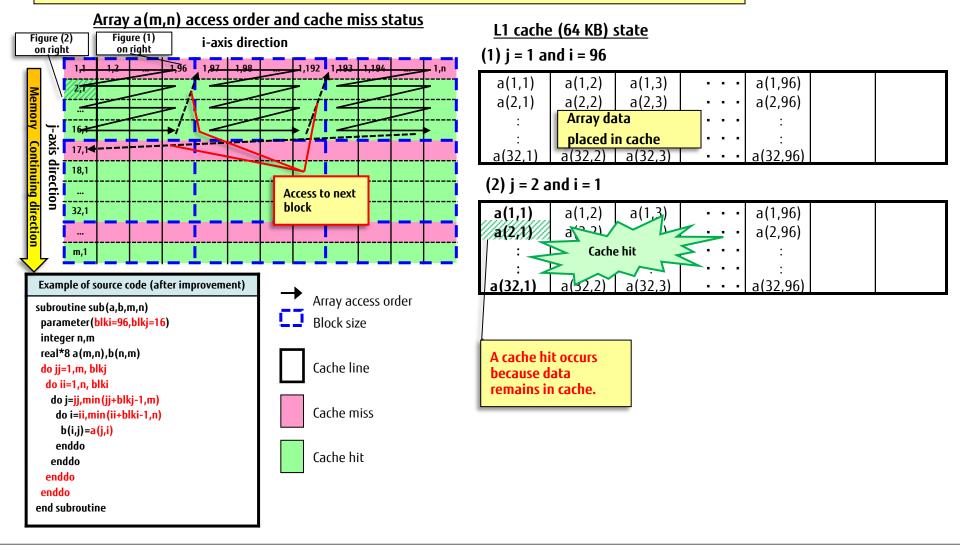

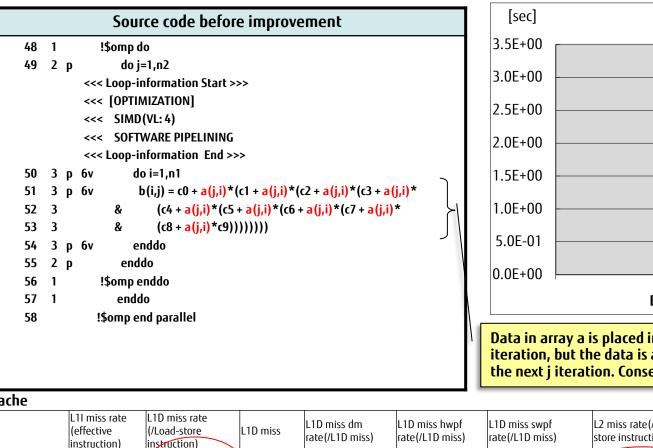

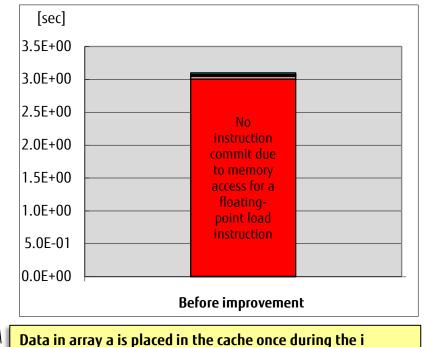

- Improvement in Data Access Wait (Improvement in Thrashing)

- Improvement in Data Access Wait (Increase in Data Locality)

- Improvement in Data Access Wait (Latency Concealment)

- Improvement in Data Access Wait (Reduced Amount of Access)

- Improvement in Operation Wait (Instruction Scheduling Improvement)

- Thread Parallelization Processing Tuning

- Thread Parallelization ratio Improvement

- Execution Efficiency Improvement of Thread Parallelization Processing

### **CPU** Tuning

- What Is CPU Tuning (Intra-Node Tuning)?

- Positioning of CPU Tuning

What Is CPU Tuning (Intra-Node Tuning)?

CPU tuning (Intra-Node tuning) improves execution efficiency on a multi-core CPU.

The types of CPU tuning are scalar tuning and thread parallelization processing tuning.

Their various approaches to improvement include source tuning, optimization control line tuning, and compiler options tuning.

#### Scalar tuning

This tuning improves execution efficiency on a multi-core CPU by focusing attention on the cores.

#### Thread parallelization processing tuning

This tuning improves the thread parallelization ratio and execution efficiency of thread parallelization processing on a multi-core CPU.

### Positioning of CPU Tuning

# How to Effectively Use PA Information and Tuning Flows

- How to Effectively Use PA Information

- Tuning Flow

- 1. Hot Spot Detection

- 2. PA Information Collection

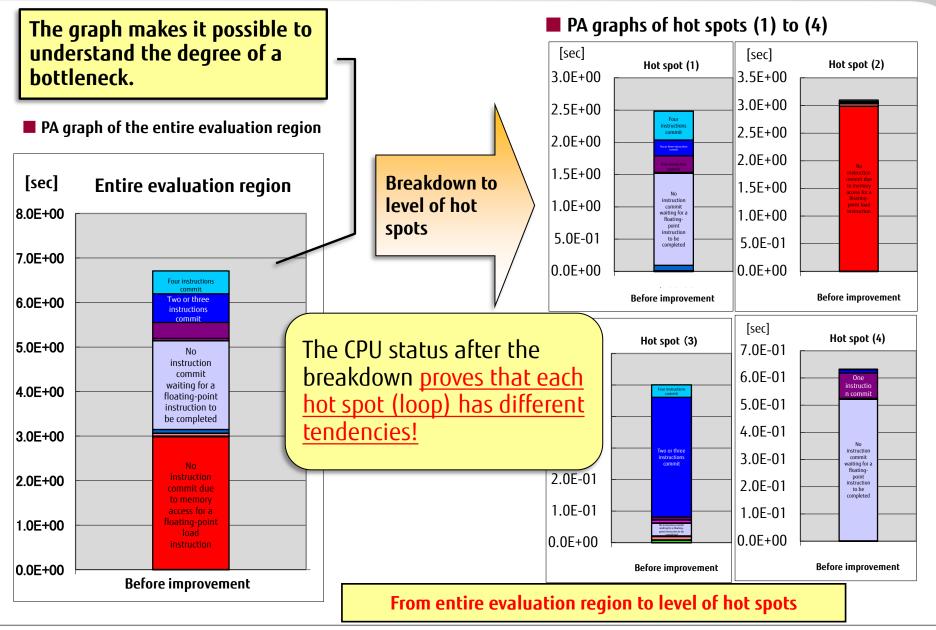

- 3. Breakdown to the Level of Hot Spots

- 4. Analysis and Diagnosis: Hot Spot (1)

- 5. Measures and Effects: Hot Spot (1)

### How to Effectively Use PA Information

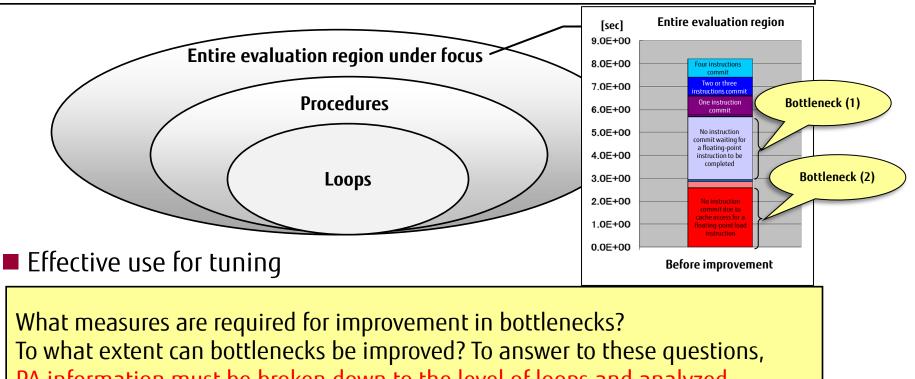

#### Understanding bottlenecks

You can determine bottlenecks in the entire evaluation region under focus (except input/output and communication), from PA information for the entire evaluation region.

PA information must be broken down to the level of loops and analyzed.

### 1. Hot Spot Detection

First, detect hot spots in the evaluation region under focus. To detect hot spots, use the sampling region specification function of fipp.

#### What is the sampling region specification function?

You can collect cost information for the specified region by using the sampling region specification function. To specify a measurement section in the source code, insert C or C++ functions or Fortran subroutines at the start and end points of cost information measurement.

|               |                   | Insertion diagram "Entire evaluation                          |

|---------------|-------------------|---------------------------------------------------------------|

| Function name | Function          | region" enclosed by sampling region                           |

| fipp_start    | Measurement start | call fipp_start() specification function<br>Evaluation region |

| fipp_stop     | Measurement end   | call fipp_stop()                                              |

|               |                   |                                                               |

- \* If the evaluation region under focus is the entire program, the sampling region specification function is not needed.

- \* For details on the sampling region specification function, see the tutorial in "Chapter 7 Tuning Tool."

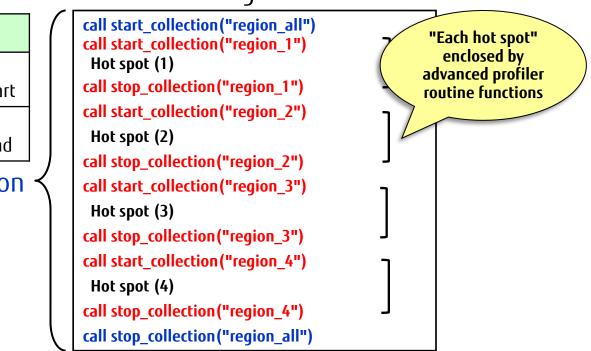

### 2. PA Information Collection

Here, collect PA information for detected hot spots. Use the advanced profiler routines of fapp (precision PA) because analysis requires highly precise PA information.

#### Advanced profiler routines (precision PA)

The routines are C and C++ functions and Fortran subroutines for specifying a measurement section for PA information. By specifying a collection section in the source code, you can collect highly precise information.

| Function name    | Function                         |

|------------------|----------------------------------|

| start_collection | Information<br>measurement start |

| stop_collection  | Information<br>measurement end   |

#### Entire evaluation region

Insertion diagram

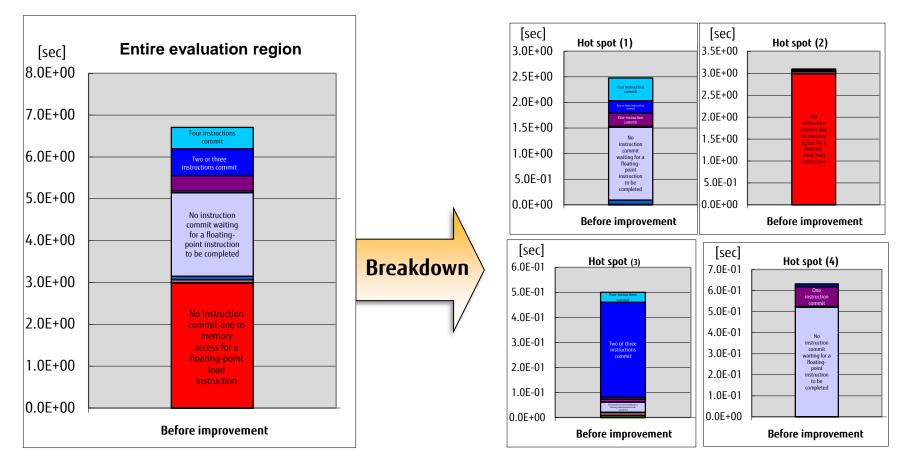

### 3. Breakdown to the Level of Hot Spots

Chapter 8 How to Effectively Use PA Information and Tuning Flows

### 4. Analysis and Diagnosis: Hot Spot (1)

ะบุ๊เารบ

### 5. Measures and Effects: Hot Spot (1)

Chapter 8 How to Effectively Use PA Information and Tuning Flows

### Analysis and Tuning of Each Hot Spot

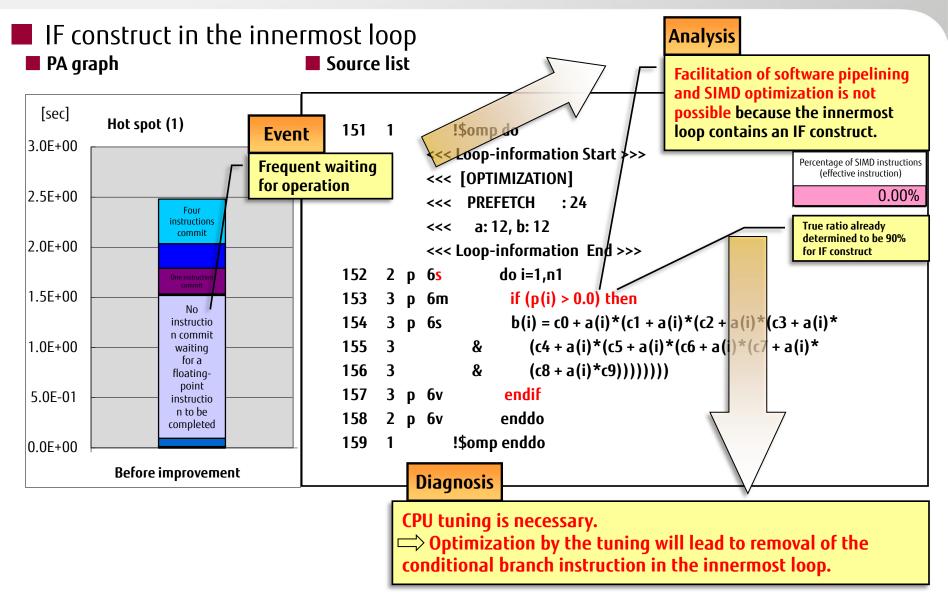

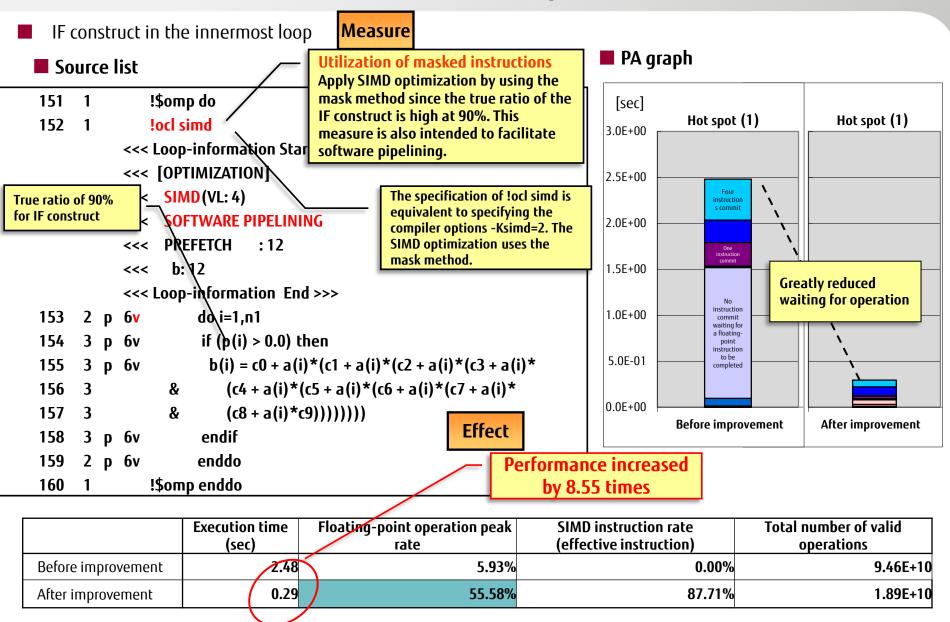

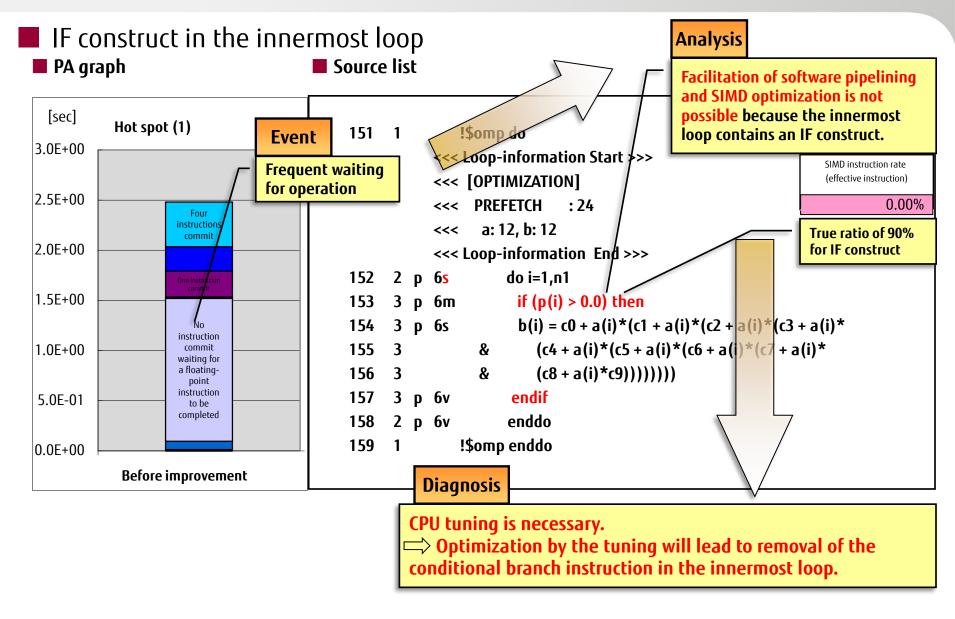

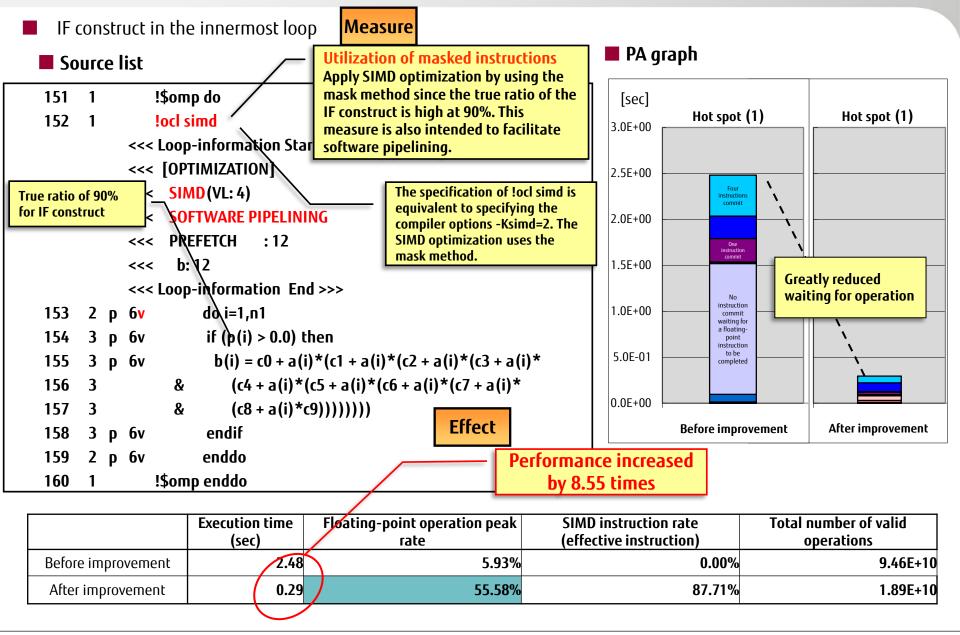

- (Duplicate) Hot Spot (1): IF Construct in the Innermost Loop (Analysis and Diagnosis)

- (Duplicate) Hot Spot (1): IF Construct in the Innermost Loop (Measures and Effects)

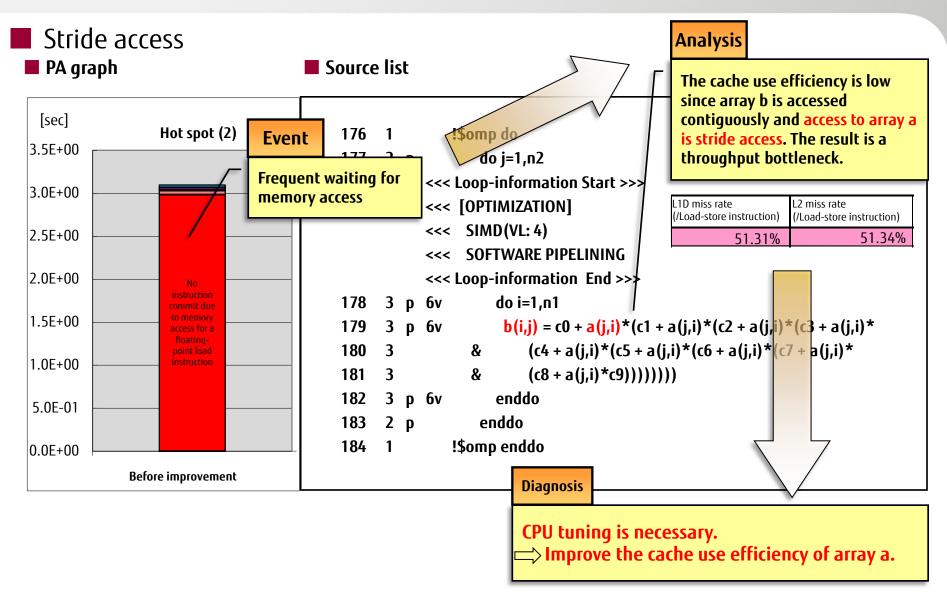

- Hot Spot (2): Stride Access (Analysis and Diagnosis)

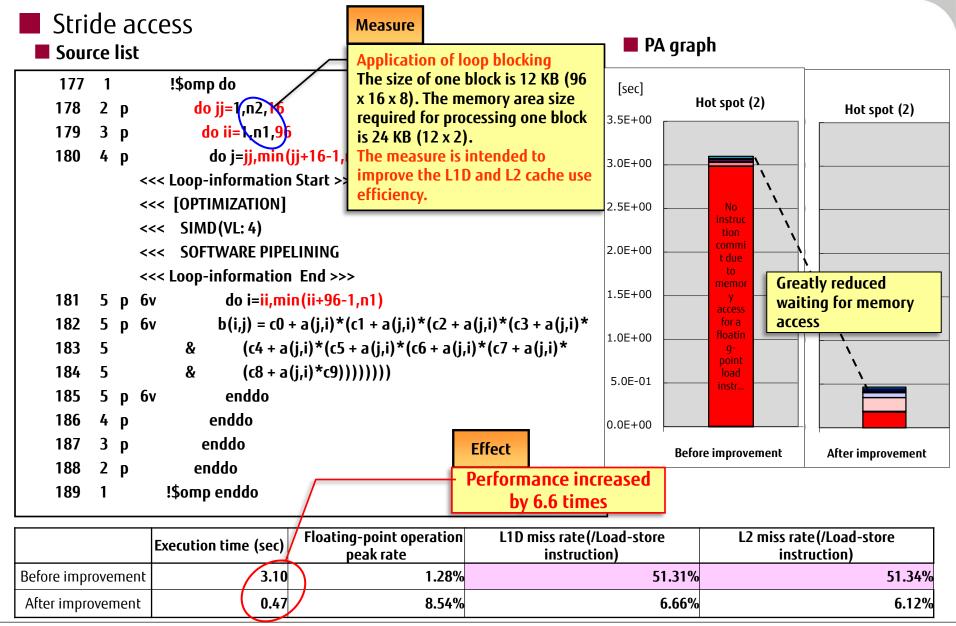

- Hot Spot (2): Stride Access (Measures and Effects)

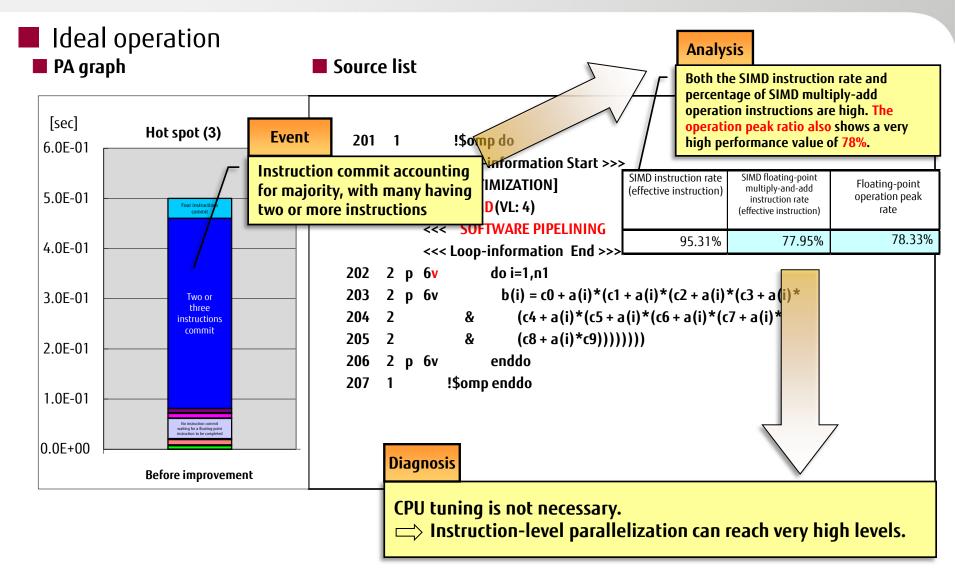

- Hot Spot (3): Ideal Operation (Analysis and Diagnosis)

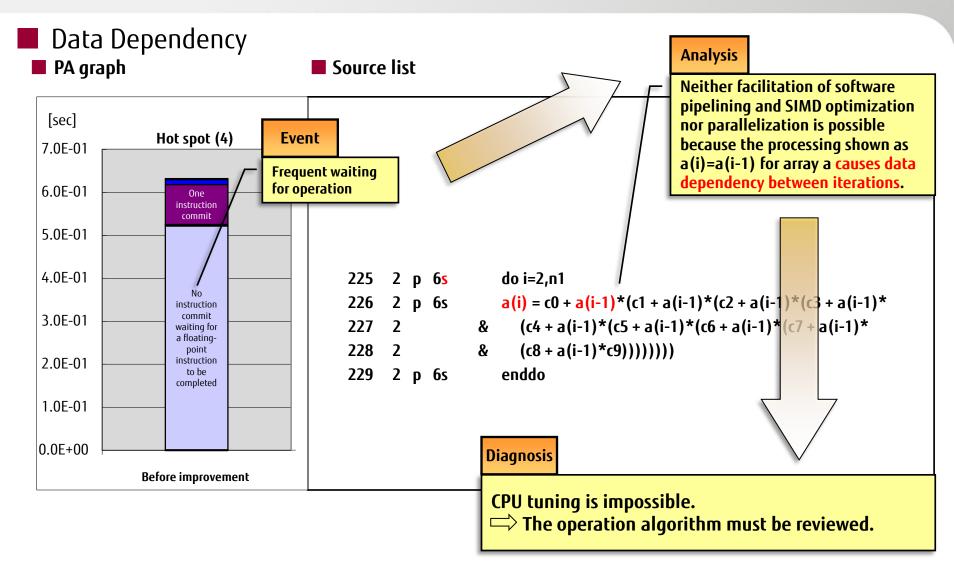

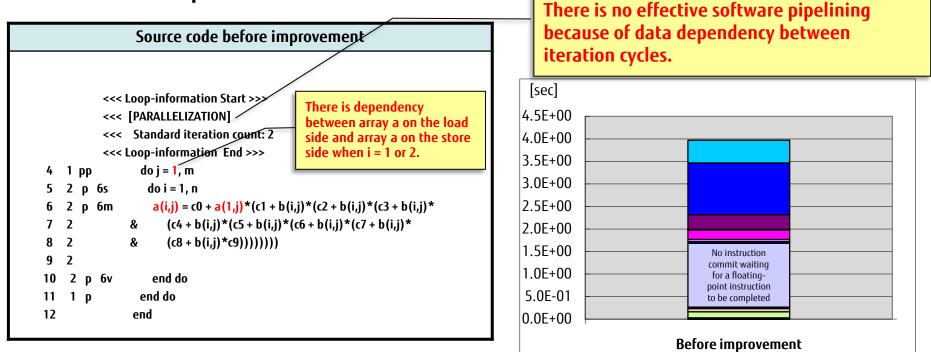

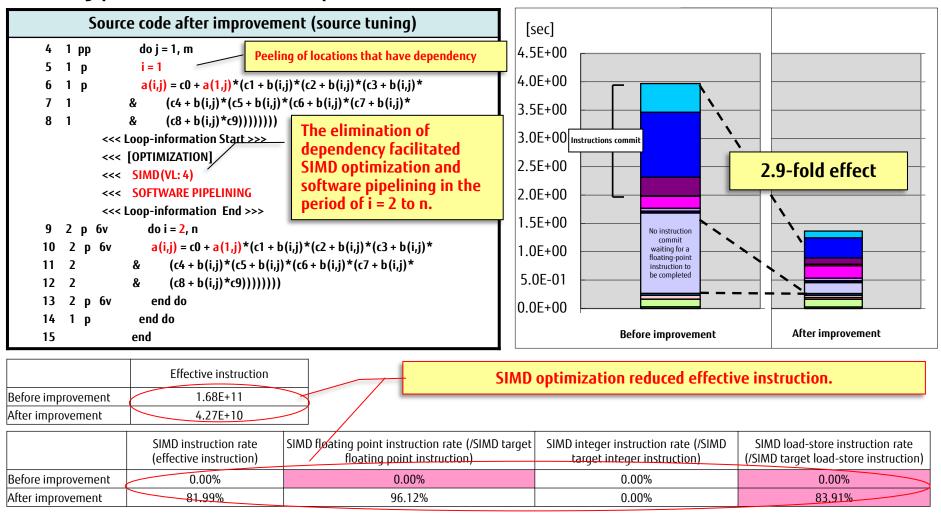

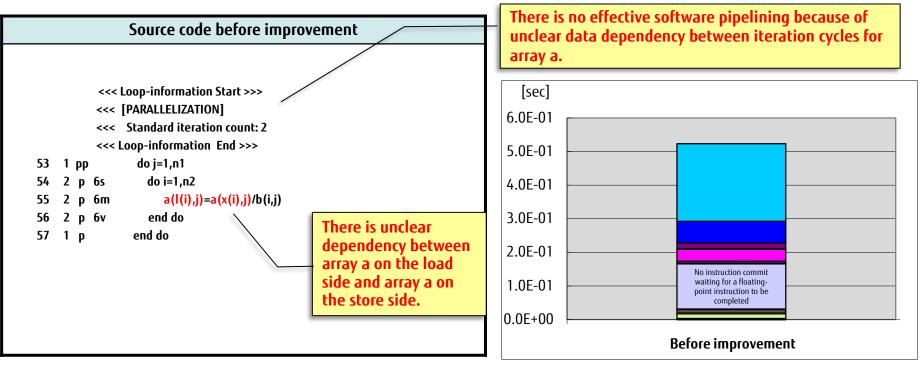

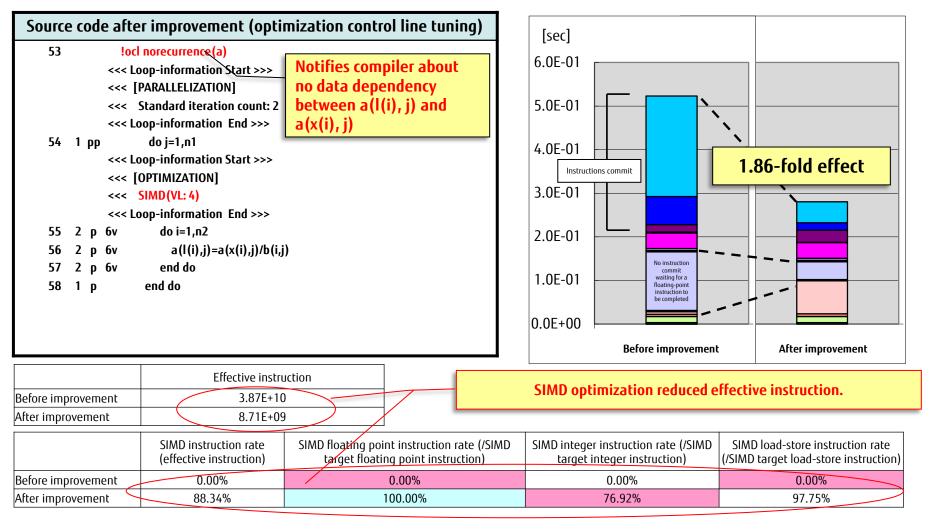

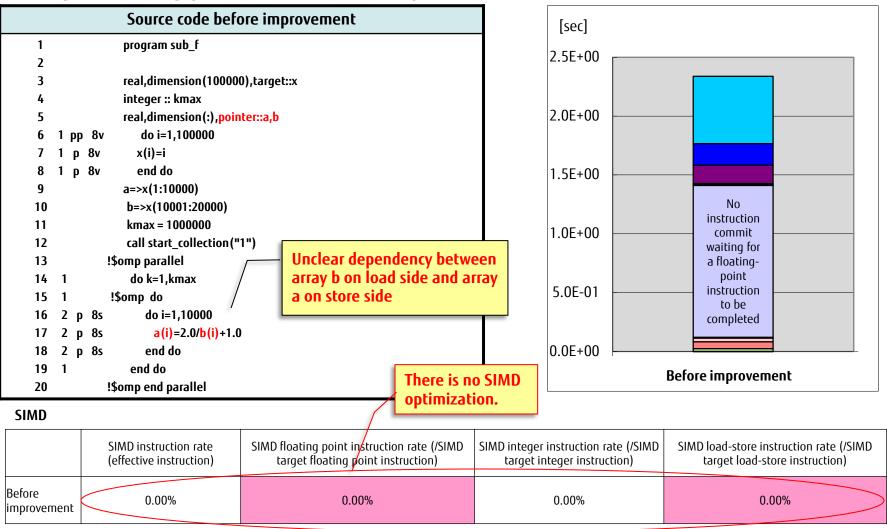

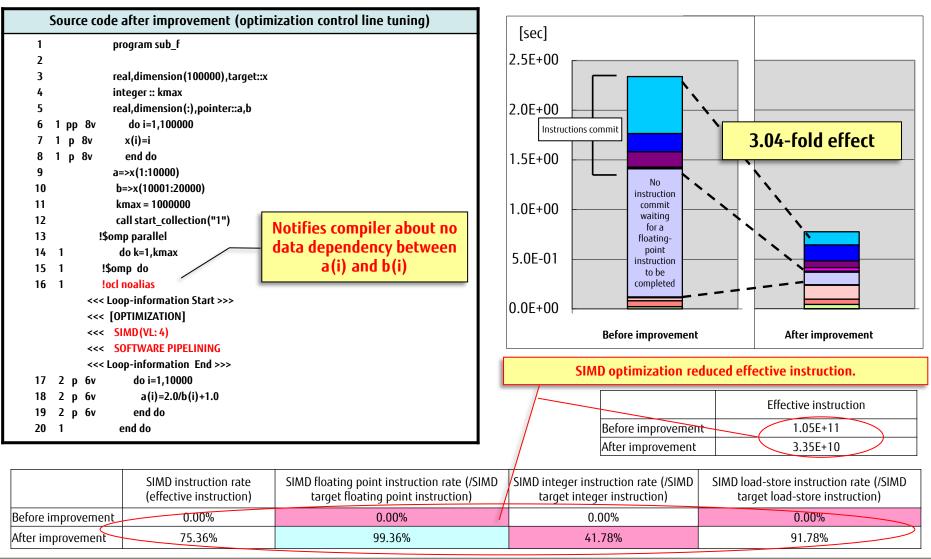

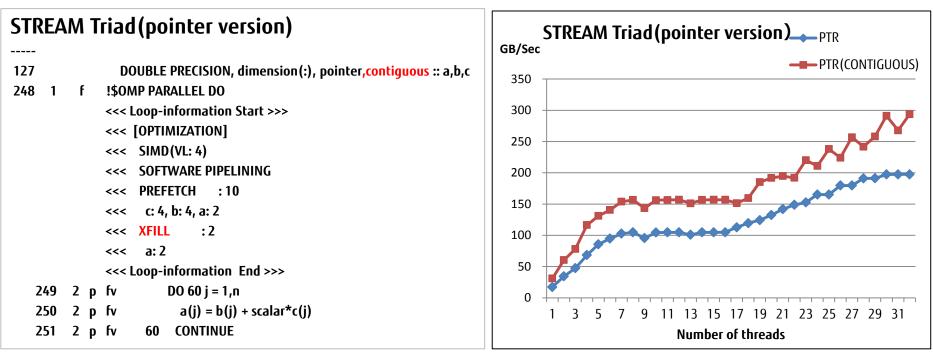

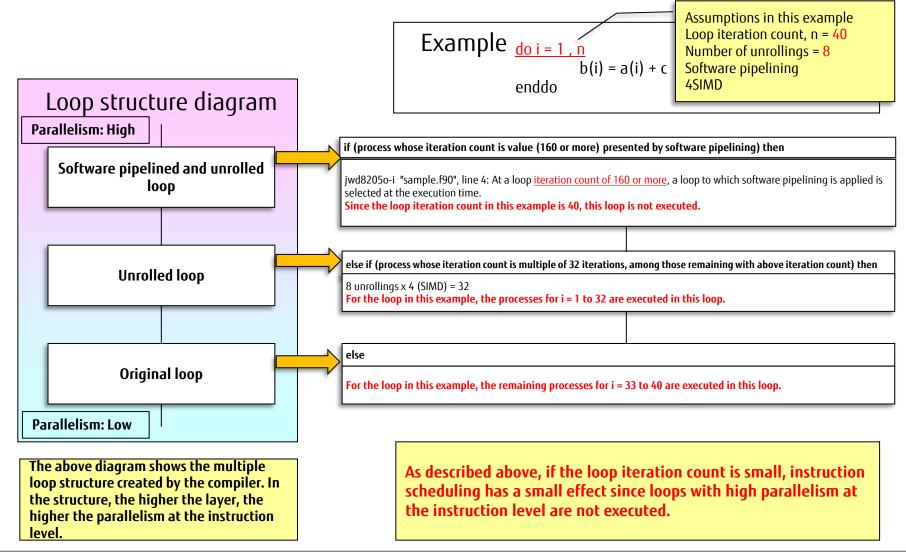

- Hot Spot (4): Data Dependency (Analysis and Diagnosis)

- Entire Evaluation Region (Measures and Effects)

- Summary

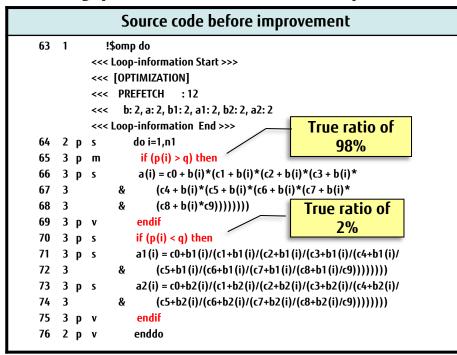

Hot Spot (1): IF Construct in the Innermost Loop (Analysis and Diagnosis)

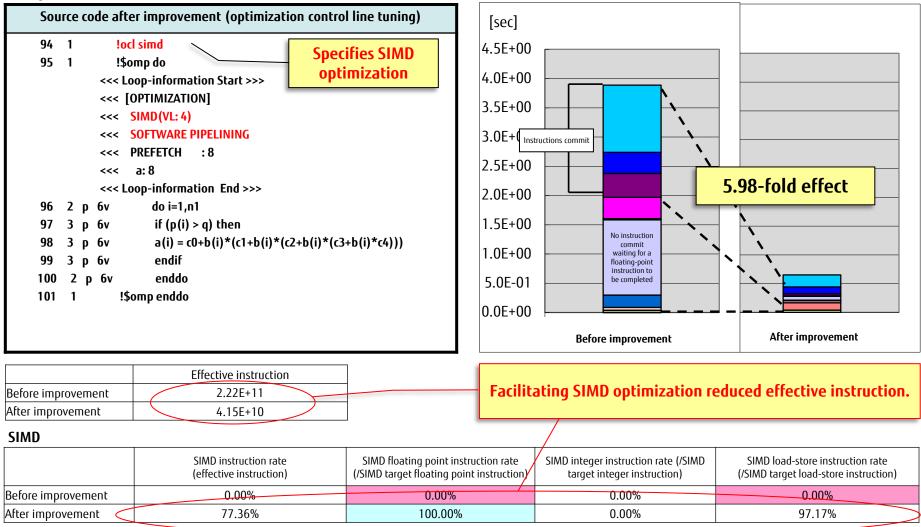

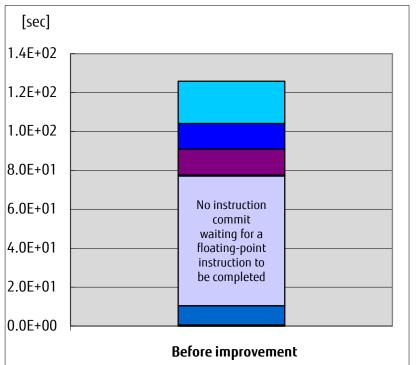

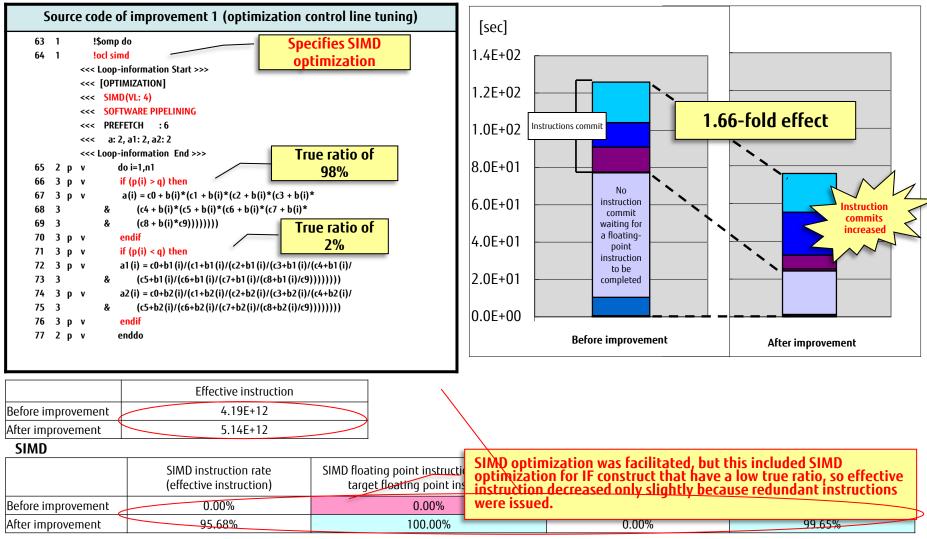

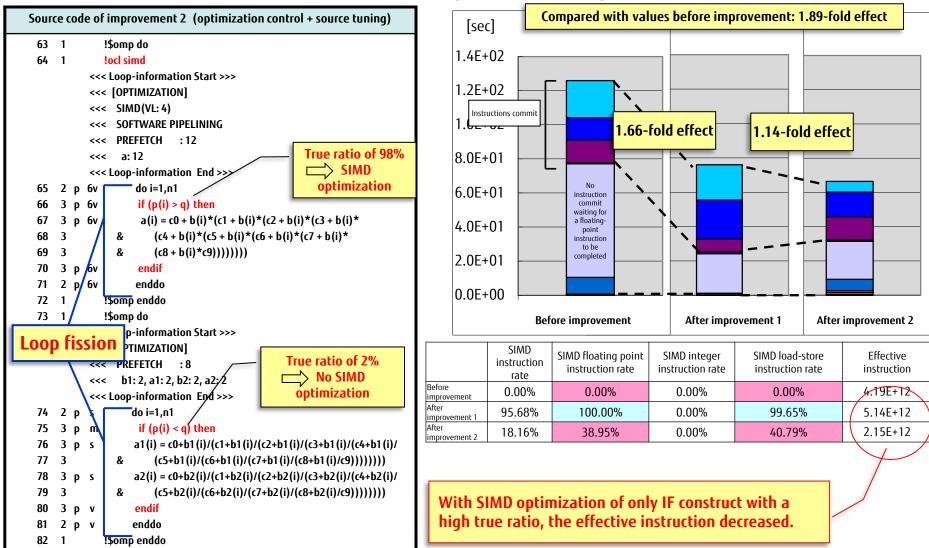

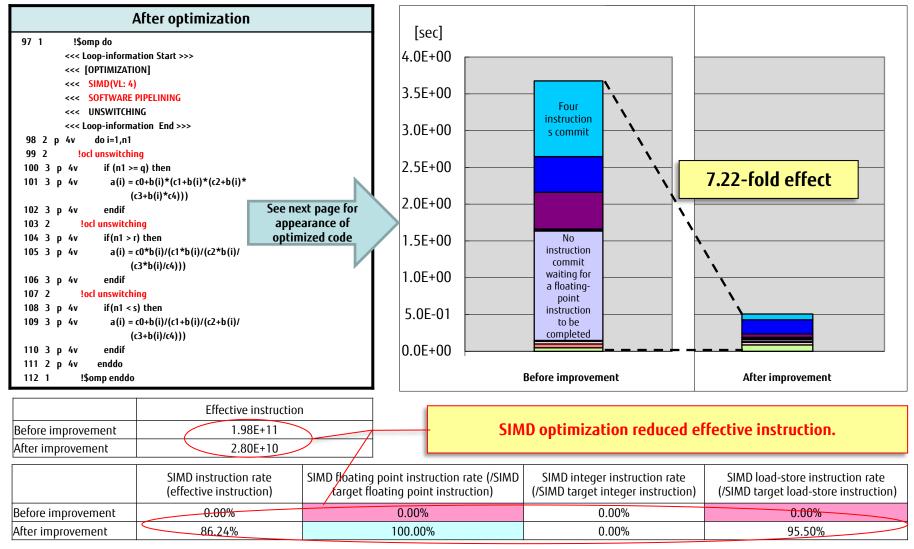

Hot Spot (1): IF Construct in the Innermost Loop (Measures and Effects)

Chapter 8 Analysis and Tuning of Each Hot Spot

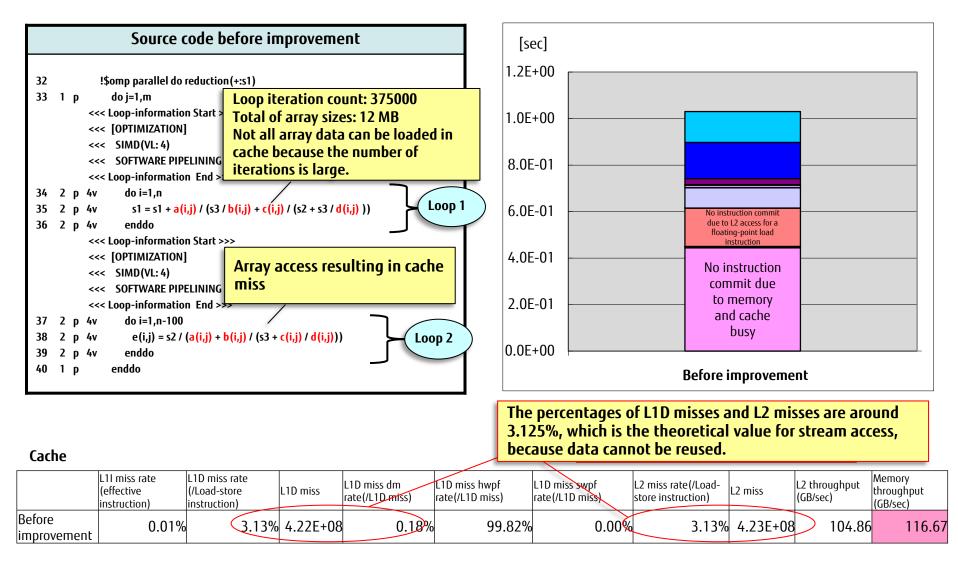

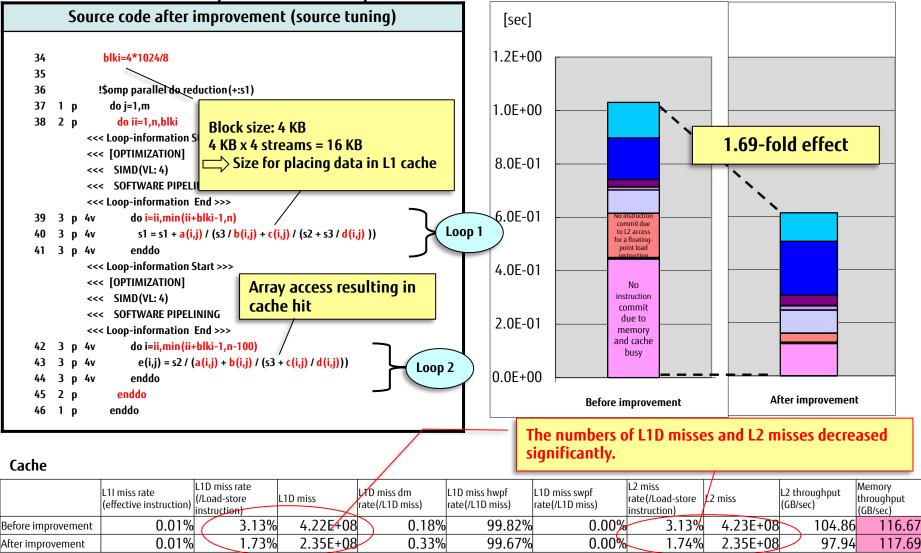

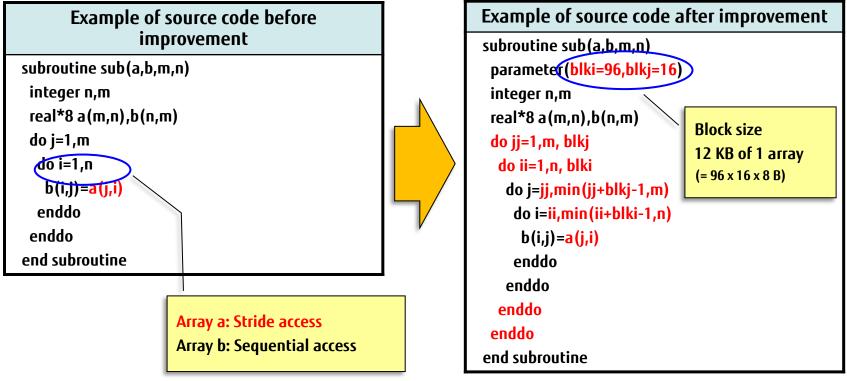

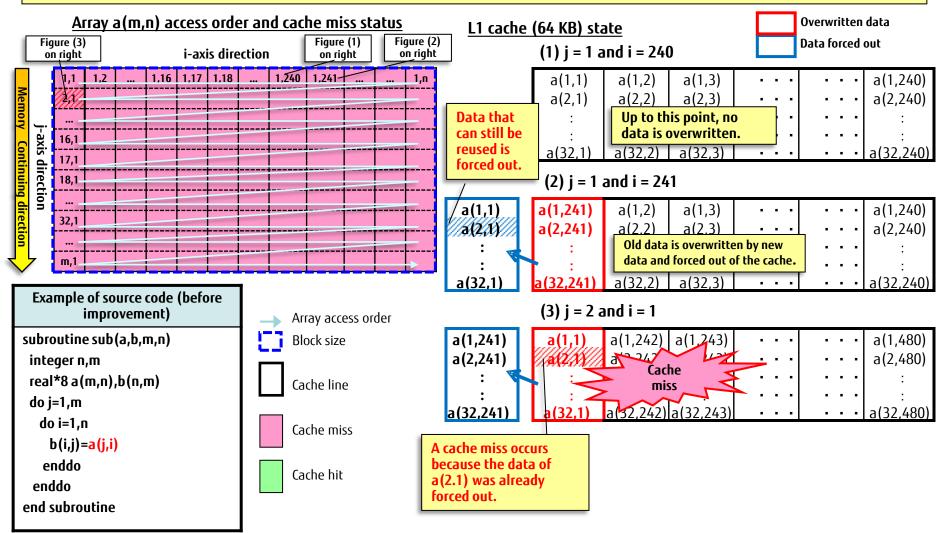

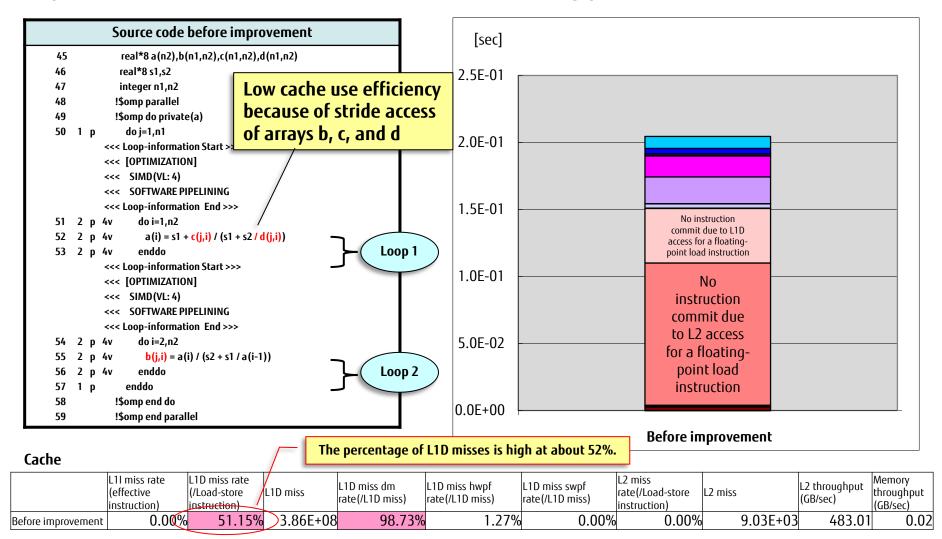

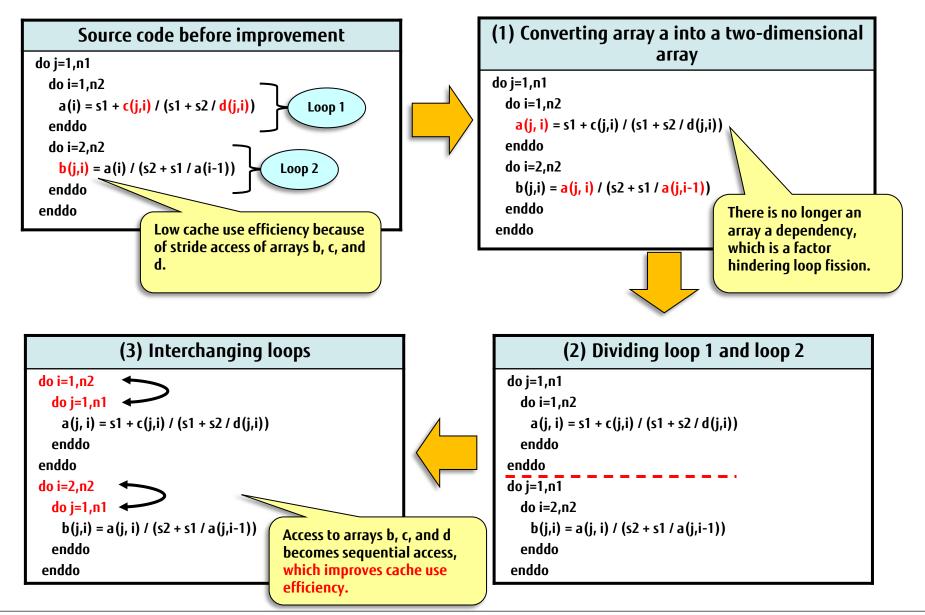

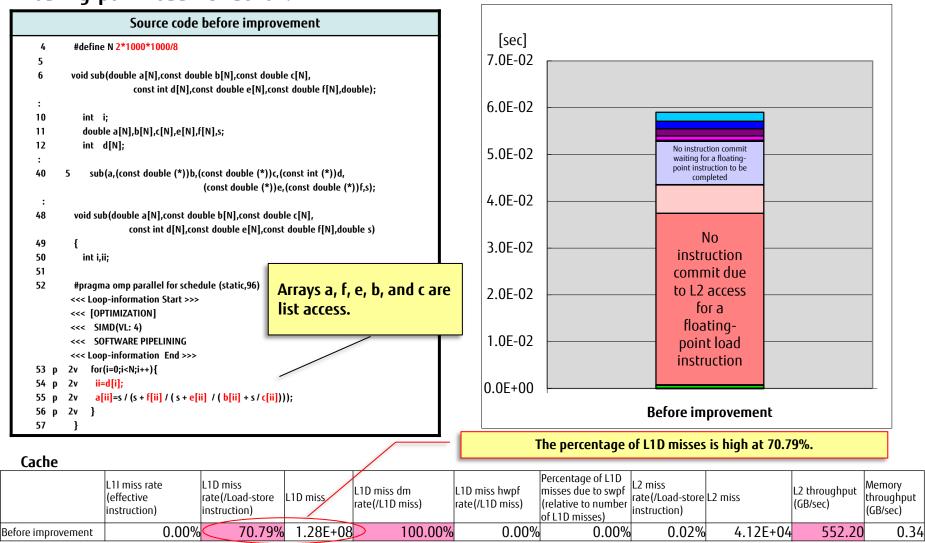

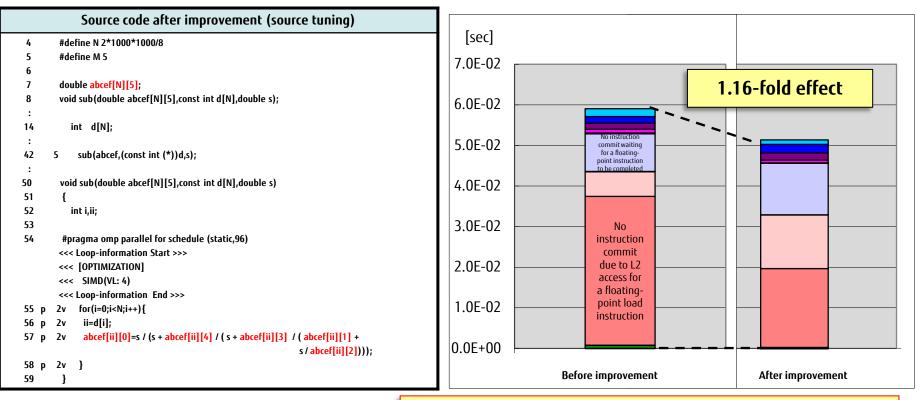

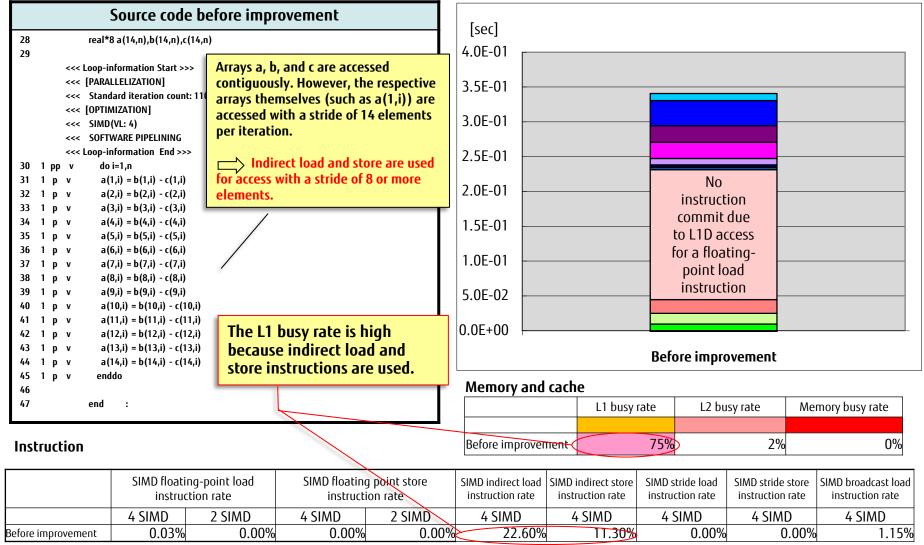

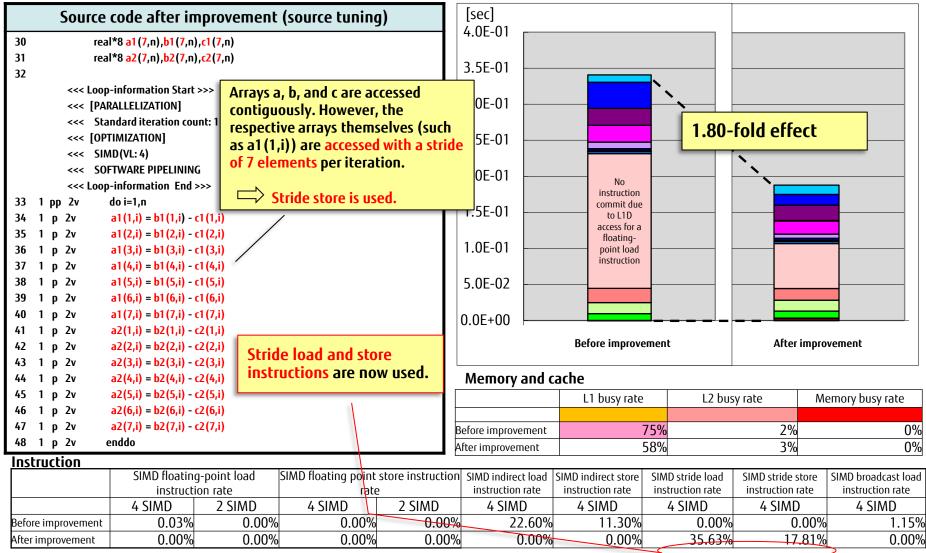

#### Hot Spot (2): Stride Access (Analysis and Diagnosis)

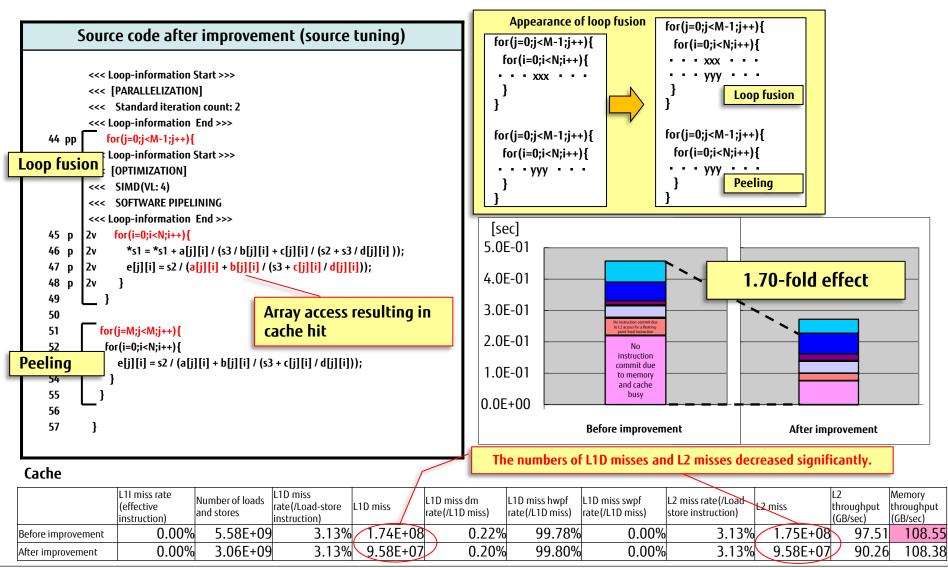

#### Hot Spot (2): Stride Access (Measures and Effects)

Chapter 8 Analysis and Tuning of Each Hot Spot

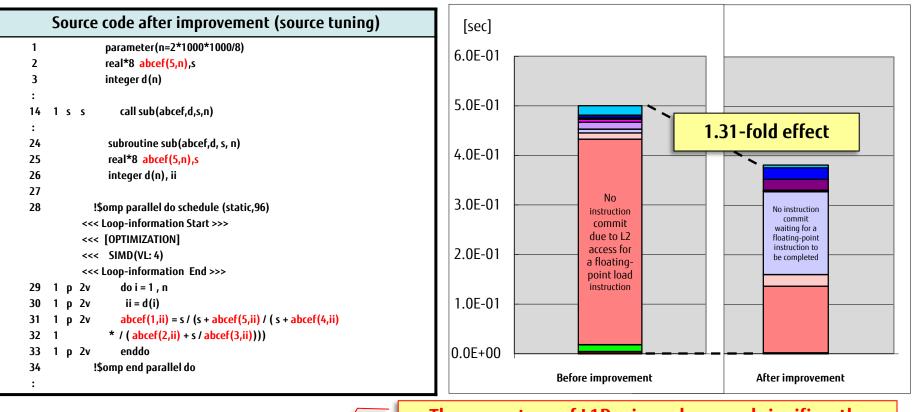

#### Hot Spot (3): Ideal Operation (Analysis and Diagnosis)

Hot Spot (4): Data Dependency (Analysis and Diagnosis)

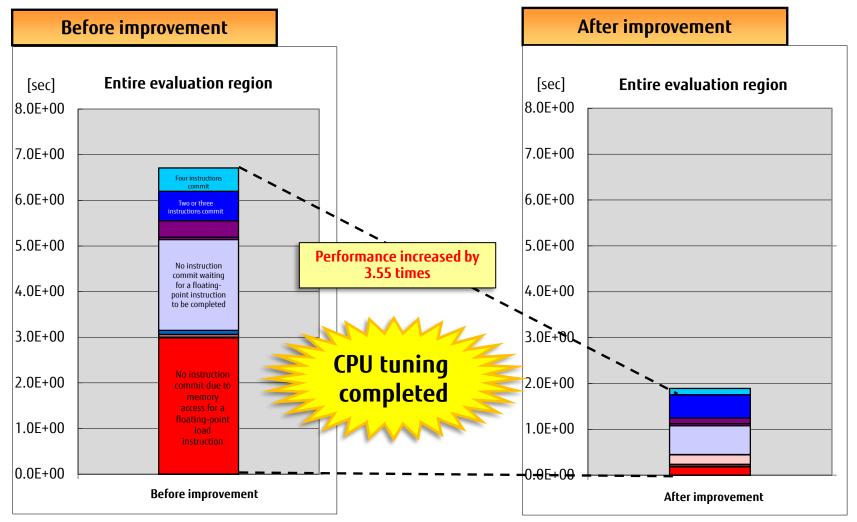

### Entire Evaluation Region (Measures and Effects)

#### 🛛 PA graph

### Summary

- You can determine bottlenecks from the PA graph of an entire evaluation region.

- The bottleneck factors are often different for every loop. For this reason, a breakdown to the level of loops is necessary to analyzing and determining whether CPU tuning is possible and how to take measures for problems.

### Navigation from PA Information to Tuning Techniques

Tuning MapTuning Technique List

### Navigation from PA Information to Tuning Techniques

- The tuning map is useful for determining a specific tuning method from PA information.

- Tuning map

- The tuning map is a list showing tuning proposals by bottleneck type. The list clearly shows what PA information to check and bottleneck factors (conditions) that occur by bottleneck classification, and summarizes the measures (tuning proposals: what to improve) for solving them.

- $\Rightarrow$  1. Identify bottleneck factors from PA information.

- $\Rightarrow$  2. Present measures (tuning proposals) for removing bottlenecks.

#### Tuning technique list

- This list summarizes various tuning techniques by tuning proposal.

Select an effective tuning technique for improvement.

- For examples of actual measures, see the scalar tuning examples.

### Tuning Map (1/12)

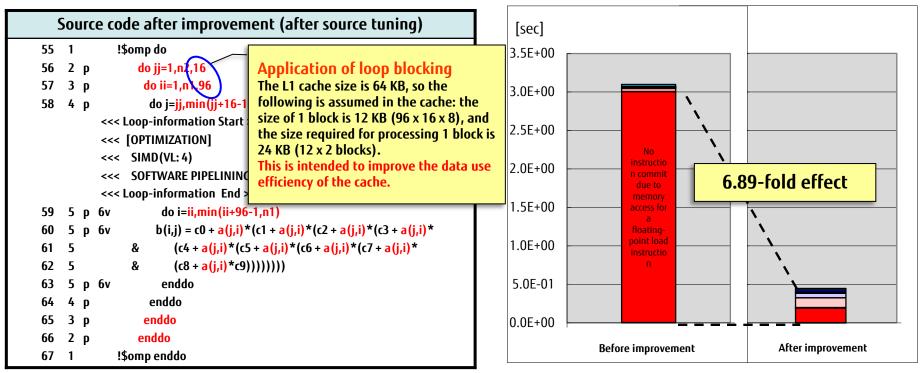

| Bottleneck classification     | High cost as seen from PA graph                                                                                 | High cost as seen from PA information                                    | Condition                                                  | Tuning proposal                                                                                                                                             |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | No instruction commit due to memory access for a floating-<br>point load instruction                            | -                                                                        | Memory latency is a bottleneck.                            | Improvement in data access wait<br>- Dimensional displacement of an array                                                                                   |

|                               | No instruction commit due to memory access for an integer<br>load instruction                                   | -                                                                        | Memory latency is a bottleneck.                            | Prefetch-related improvement Improvement in data access wait     Dimensional displacement of an array     Prefetch-related improvement                      |

|                               | No instruction commit because SP (store port) is full                                                           | -                                                                        | The store instruction cost is a bottleneck.                | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Prefetch-related improvement<br>- High-speed store (XFILL)                   |

| lemory bottleneck             | No instruction commit due to memory and cache busy                                                              | -                                                                        | Memory throughput is a bottleneck.                         | Improvement in data access wait     Improvement in data access wait     Dimensional displacement of an array     Loop blocking     High-speed store (XFILL) |

|                               | -                                                                                                               | High memory busy rate                                                    | Memory throughput is a bottleneck.                         | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Loop blocking<br>- High-speed store (XFILL)                                  |

|                               | -                                                                                                               | High percentage of L2 misses<br>High percentage of L2 misses due to dm   | Memory latency is a bottleneck.                            | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Loop blocking<br>- Prefetch-related improvement<br>- Thrashing               |

|                               | No instruction commit due to L2 access for a floating-point load instruction                                    | -                                                                        | L2 cache latency is a bottleneck.                          | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Prefetch-related improvement                                                 |

|                               | No instruction commit due to L2 access for an integer load instruction                                          | -                                                                        | L2 cache latency is a bottleneck.                          | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Prefetch-related improvement                                                 |

| 2 cache bottleneck            | -                                                                                                               | High L2 busy rate                                                        | L2 cache throughput is a bottleneck.                       | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Loop blocking                                                                |

|                               | -                                                                                                               | High percentage of L1D misses<br>High percentage of L1D misses due to dm | L2 cache latency is a bottleneck.                          | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Thrashing                                                                    |

|                               | No instruction commit due to L1D access for a floating-<br>point load instruction                               | -                                                                        | L1 cache latency is a bottleneck.                          | Instruction scheduling improvement                                                                                                                          |

| 1 cache bottleneck            | No instruction commit due to L1D access for an integer load instruction                                         | -                                                                        | L1 cache latency is a bottleneck.                          | Instruction scheduling improvement                                                                                                                          |

|                               | -                                                                                                               | High L1 busy rate                                                        | L1 cache throughput is a bottleneck.                       | Improvement in data access wait<br>- Algorithm review                                                                                                       |

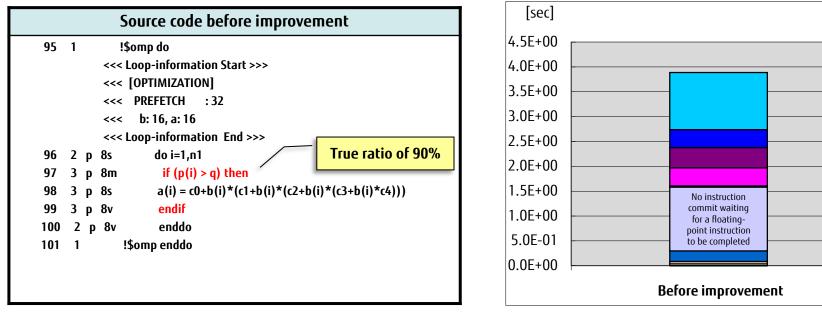

|                               | No instruction commit waiting for a floating-point instruction to be completed                                  | -                                                                        | Operation instruction latency is a bottleneck.             | Instruction scheduling improvement                                                                                                                          |

| cheduling<br>ottleneck        | No instruction commit waiting for an integer instruction to be<br>completed                                     | -                                                                        | Operation instruction latency is a bottleneck.             | Instruction scheduling improvement                                                                                                                          |

|                               | No instruction commit waiting for a branch instruction to be completed                                          | -                                                                        | A branch instruction is a bottleneck.                      | Instruction scheduling improvement<br>- IF statement removal<br>- Masked SIMD                                                                               |

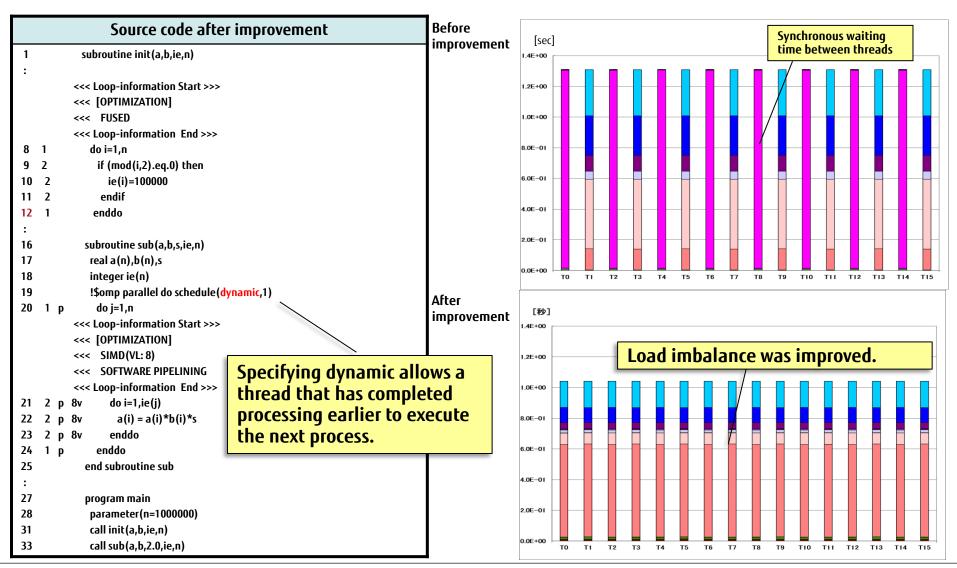

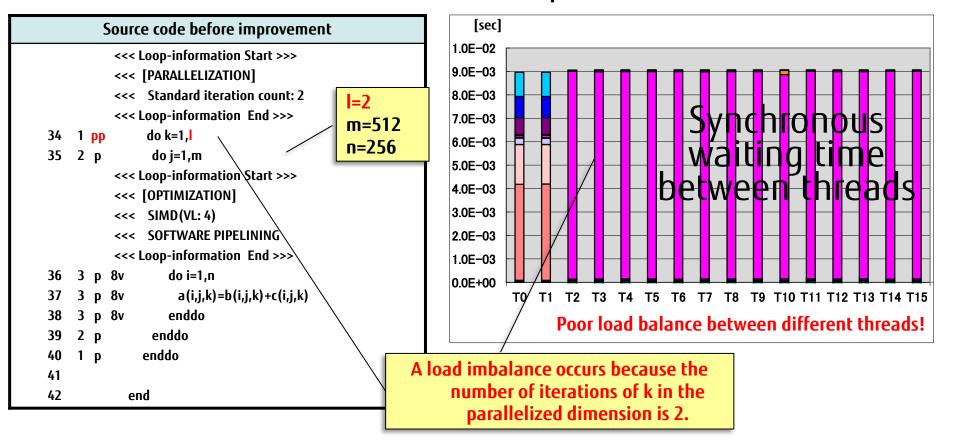

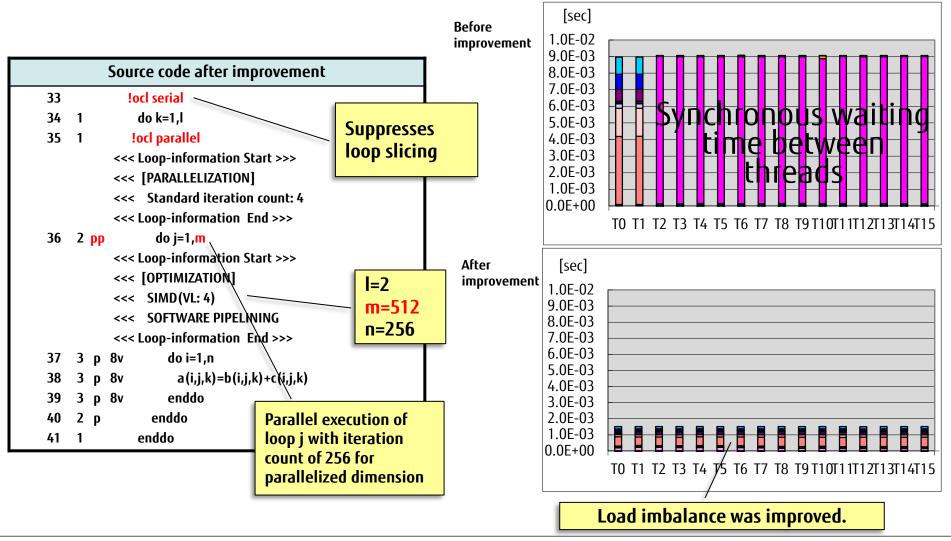

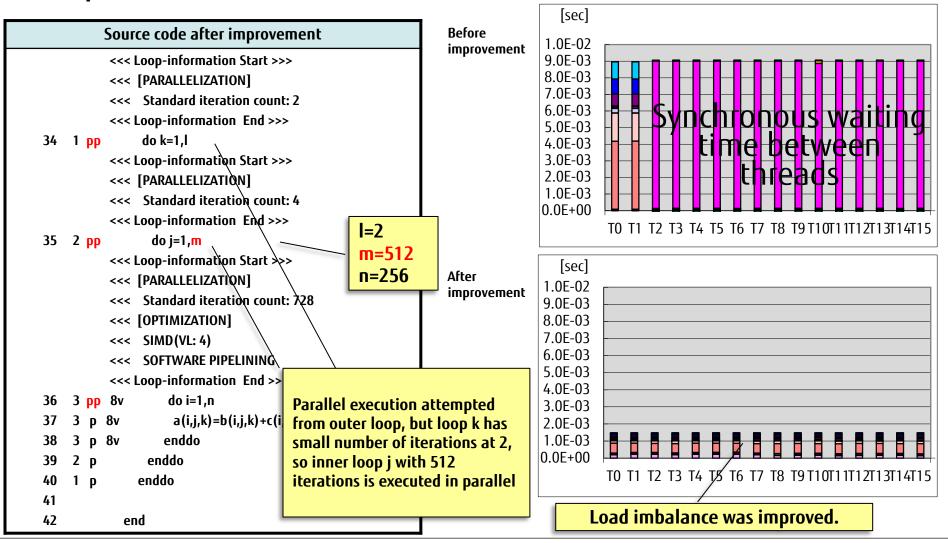

| arallelization bottleneck     | Synchronous waiting time between threads                                                                        | -                                                                        | A part that is not thread parallelization is a bottleneck. |                                                                                                                                                             |

| oad imbalance bottleneck      | Synchronous waiting time between threads                                                                        | Large difference in the instruction balance between max and min          | A load imbalance between threads is a bottleneck.          | parallelization processing                                                                                                                                  |

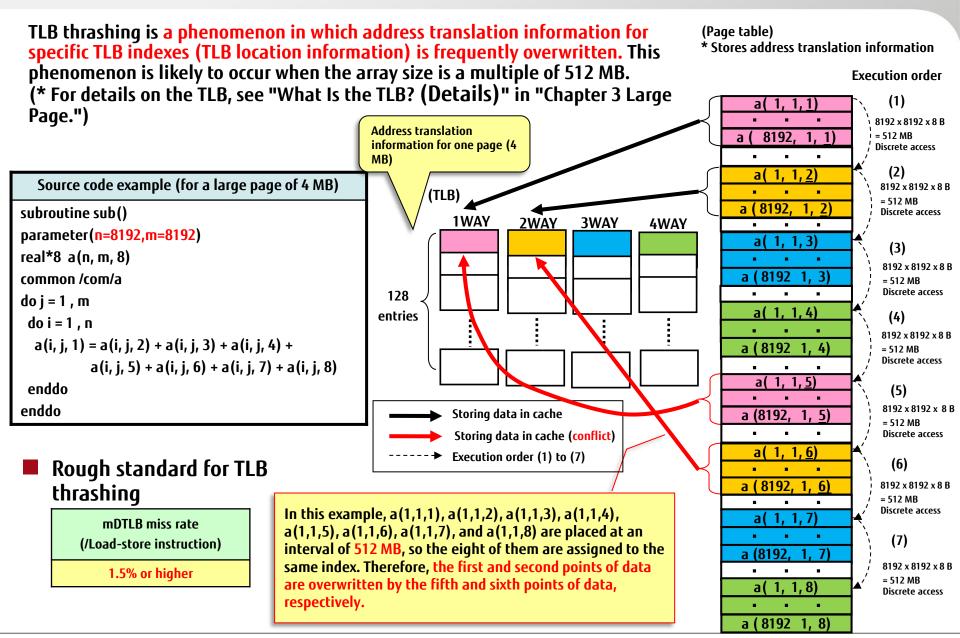

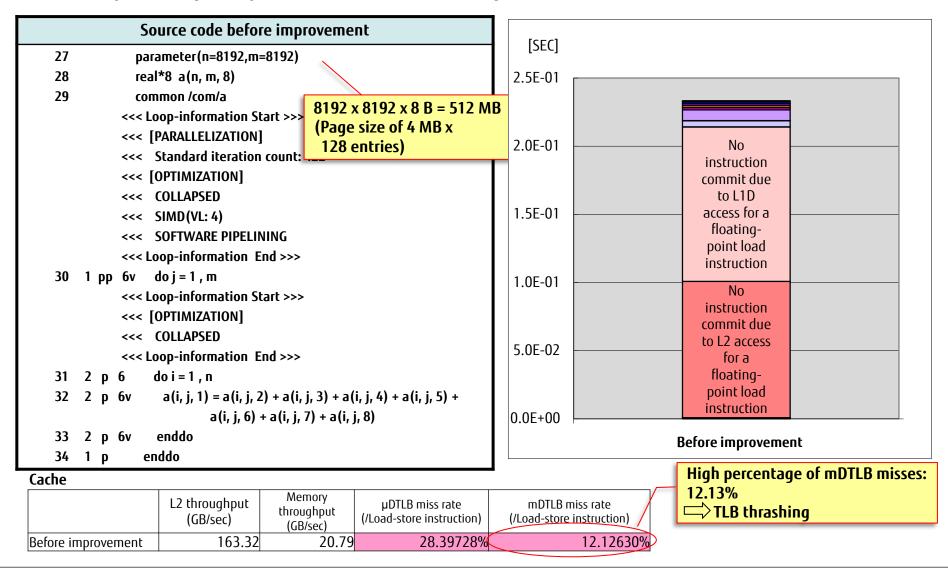

| TLB bottleneck                | -                                                                                                               | High percentage of mDTLB misses                                          | TLB misses and TLB thrashing are a bottleneck.             | Improvement in the TLB bottleneck<br>- Elimination of thrashing<br>- Change of areas used<br>- Optimization using large page options                        |

|                               | -                                                                                                               | High percentage of uDTLB misses                                          | TLB misses are a bottleneck.                               | Improvement in the TLB bottleneck<br>- Page size expansion                                                                                                  |

| nstruction fetch              | No instruction commit waiting for an instruction to be<br>fetched                                               | -                                                                        | Instruction cache misses and thrashing are a bottleneck.   | Improvement in instruction fetch<br>- Reduction in the loop body<br>- Algorithm review<br>- Elimination of thrashing                                        |

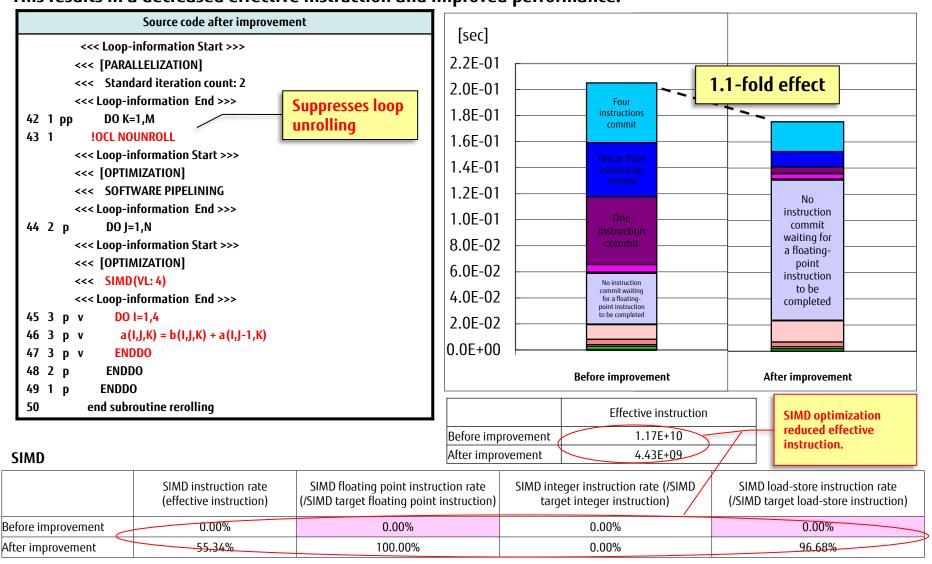

| nstruction count<br>ottleneck | Four instructions commit<br>Instruction<br>Two or three instructions commit<br>commit<br>One instruction commit | -                                                                        | The number of instructions is a bottleneck.                | Improvement in the instruction count bottleneck<br>- Facilitation of SIMD optimization<br>- Prefetch-related improvement<br>- Inline expansion              |

Chapter 8 Navigation from PA Information to Tuning Techniques

### Tuning Map (2/12)

#### Bottleneck classifications

|                                                                  | No instruction commit due to memory access for a floating-point load instruction                                                            |  |  |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Momony bottlopock                                                | No instruction commit due to memory access for an integer load instruction                                                                  |  |  |

| Memory bottleneck                                                | No instruction commit because SP (store port) is full                                                                                       |  |  |

|                                                                  | No instruction commit due to memory and cache busy                                                                                          |  |  |

|                                                                  | No instruction commit due to L2 access for a floating-point load instruction                                                                |  |  |

| L2 cache bottleneck                                              | No instruction commit due to L2 access for an integer load instruction                                                                      |  |  |

| 1                                                                | No instruction commit due to L1D access for a floating-point load instruction                                                               |  |  |

| L1 cache bottleneck                                              | No instruction commit due to L1D access for an integer load instruction                                                                     |  |  |

|                                                                  | No instruction commit waiting for a floating-point instruction to be completed                                                              |  |  |

| Scheduling bottleneck                                            | No instruction commit waiting for an integer instruction to be completed                                                                    |  |  |

|                                                                  | No instruction commit waiting for a branch instruction to be completed                                                                      |  |  |

|                                                                  | Synchronous waiting time between threads                                                                                                    |  |  |

| Parallelization bottleneck                                       | Synchronous waiting time between threads                                                                                                    |  |  |

| Parallelization bottleneck<br>Load imbalance bottleneck          | Synchronous waiting time between threads<br>Synchronous waiting time between threads                                                        |  |  |

|                                                                  |                                                                                                                                             |  |  |

| Load imbalance bottleneck                                        |                                                                                                                                             |  |  |

| Load imbalance bottleneck<br>TLB bottleneck<br>Instruction fetch | Synchronous waiting time between threads<br>-<br>No instruction commit waiting for an instruction to be fetched<br>Four instructions commit |  |  |

| Load imbalance bottleneck<br>TLB bottleneck                      | Synchronous waiting time between threads<br>-<br>No instruction commit waiting for an instruction to be fetched<br>Four instructions commit |  |  |

Left: Bottleneck classifications Right: Costs as seen from PA graph

Chapter 8 Navigation from PA Information to Tuning Techniques

### Tuning Map (3/12)

#### Memory bottleneck

| High cost as seen from PA<br>graph                                               | High cost as seen from PA information                                     | Condition                                   | Tuning proposal                                                                                                                               |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| No instruction commit due to memory access for a floating-point load instruction | -                                                                         | Memory latency is a bottleneck.             | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Prefetch-related improvement                                   |

| No instruction commit due to memory access for an integer load instruction       | _                                                                         | Memory latency is a bottleneck.             | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Prefetch-related improvement                                   |

| No instruction commit<br>because SP (store port) is full                         |                                                                           | The store instruction cost is a bottleneck. | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Prefetch-related improvement<br>- High-speed store (XFILL)     |

| No instruction commit due to memory and cache busy                               |                                                                           | Memory throughput is a<br>bottleneck.       | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Loop blocking<br>- High-speed store (XFILL)                    |

| -                                                                                | High memory busy rate                                                     | Memory throughput is a<br>bottleneck.       | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Loop blocking<br>- High-speed store (XFILL)                    |

| -                                                                                | High percentage of L2 misses<br>High percentage of L2 misses<br>due to dm | Memory latency is a bottleneck.             | Improvement in data access wait<br>- Dimensional displacement of an array<br>- Loop blocking<br>- Prefetch-related improvement<br>- Thrashing |

FUJITSU

### Tuning Map (4/12)

#### L2 cache bottleneck

| High cost as seen from<br>PA graph            | High cost as seen from<br>PA information                                       | Condition                               | Tuning proposal                                                                                                                             |

|-----------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| No instruction commit due to L2 access for a  | _                                                                              | L2 cache latency is a bottleneck.       | Improvement in data access wait<br>- Dimensional displacement of an                                                                         |

| floating-point load<br>instruction            |                                                                                |                                         | array<br>- Prefetch-related improvement                                                                                                     |

| No instruction commit due to L2 access for an | _                                                                              | L2 cache latency is a bottleneck.       | Improvement in data access wait<br>- Dimensional displacement of an                                                                         |

| integer load instruction                      |                                                                                |                                         | array<br>- Prefetch-related improvement                                                                                                     |

| -                                             |                                                                                | L2 cache throughput is a<br>bottleneck. | Improvement in data access wait<br>- Dimensional displacement of an<br>array<br>- Loop blocking                                             |

| -                                             | High percentage of L1D<br>misses<br>High percentage of L1D<br>misses due to dm | L2 cache latency is a bottleneck.       | <ul> <li>Loop blocking</li> <li>Improvement in data access wait</li> <li>Dimensional displacement of an array</li> <li>Thrashing</li> </ul> |

FUJITSU

### Tuning Map (5/12)

#### L1 cache bottleneck

| High cost as seen from PA graph | PA information     | Condition                               | Tuning proposal                                       |

|---------------------------------|--------------------|-----------------------------------------|-------------------------------------------------------|

| No instruction commit due       |                    | L1 cache latency is a bottleneck.       | Instruction scheduling                                |

| to L1D access for a             | _                  |                                         | improvement                                           |

| floating-point load             | -                  |                                         |                                                       |

| instruction                     |                    |                                         |                                                       |

| No instruction commit due       |                    | L1 cache latency is a bottleneck.       | Instruction scheduling                                |

| to L1D access for an            | -                  |                                         | improvement                                           |

| integer load instruction        |                    |                                         |                                                       |

| -                               | lligh 11 hugy rate | L1 cache throughput is a<br>bottleneck. | Improvement in data access wait<br>- Algorithm review |

### Tuning Map (6/12)

#### Scheduling bottleneck

| High cost as seen from<br>PA graph                                                       | High cost as seen from<br>PA information | Condition                                      | Tuning proposal                                                                  |

|------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------|

| No instruction commit<br>waiting for a floating-<br>point instruction to be<br>completed |                                          | Operation instruction latency is a bottleneck. | Instruction scheduling<br>improvement                                            |

| No instruction commit<br>waiting for an integer<br>instruction to be<br>completed        |                                          | Operation instruction latency is a bottleneck. | Instruction scheduling<br>improvement                                            |

| No instruction commit<br>waiting for a branch<br>instruction to be<br>completed          |                                          |                                                | Instruction scheduling<br>improvement<br>- IF statement removal<br>- Masked SIMD |

### Tuning Map (7/12)

#### Parallelization bottleneck

| High cost as seen from PA<br>graph          | High cost as seen from<br>PA information | Condition | Tuning proposal                             |

|---------------------------------------------|------------------------------------------|-----------|---------------------------------------------|

| Synchronous waiting time<br>between threads |                                          | ·         | Thread parallelization ratio<br>improvement |

### Tuning Map (8/12)

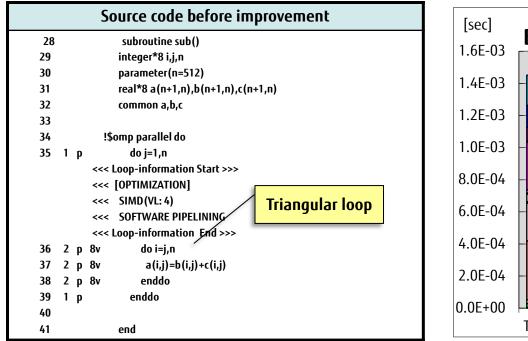

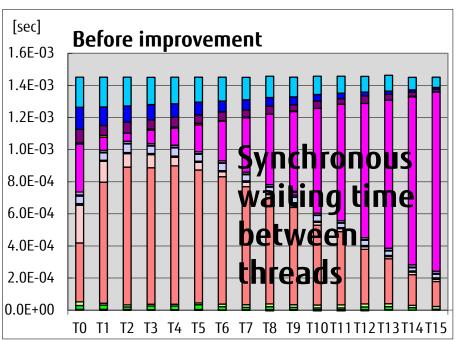

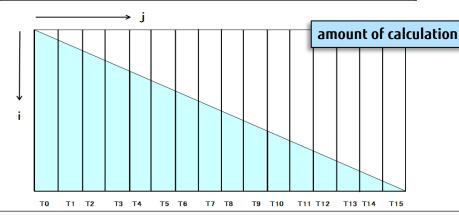

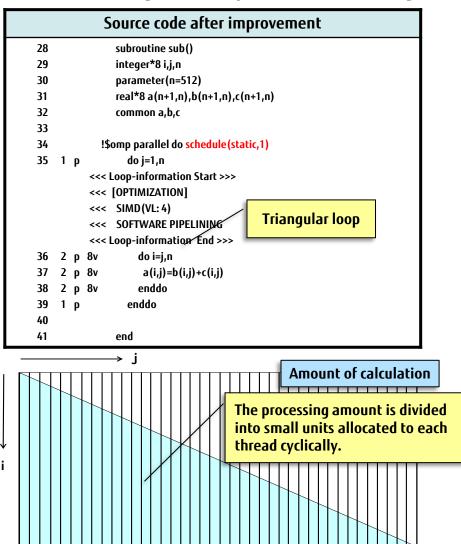

#### Load imbalance bottleneck

| High cost as seen from<br>PA graph | High cost as seen from PA information | Condition                | Tuning proposal                                                             |

|------------------------------------|---------------------------------------|--------------------------|-----------------------------------------------------------------------------|

| time between threads               |                                       | threads is a bottleneck. | Execution efficiency<br>improvement of thread<br>parallelization processing |

### Tuning Map (9/12)

| TLB bottleneck                                                             |                                    |                                                   |                                                                                                                                      |  |

|----------------------------------------------------------------------------|------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| High cost as seen from<br>PA graphHigh cost as seen from<br>PA information |                                    | Condition                                         | Tuning proposal                                                                                                                      |  |

|                                                                            |                                    | TLB misses and TLB thrashing<br>are a bottleneck. | Improvement in the TLB bottleneck<br>- Elimination of thrashing<br>- Change of areas used<br>- Optimization using large page options |  |

|                                                                            | High percentage of<br>uDTLB misses | TLB misses are a bottleneck.                      | Improvement in the TLB bottleneck<br>- Page size expansion                                                                           |  |

FUJITSU

### Tuning Map (10/12)

#### Instruction fetch

| High cost as seen from<br>PA graph                                   | High cost as seen from PA information | Condition                                                   | Tuning proposal                                                                                                      |

|----------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| No instruction commit<br>waiting for an instruction<br>to be fetched |                                       | Instruction cache misses and<br>thrashing are a bottleneck. | Improvement in instruction fetch<br>- Reduction in the loop body<br>- Algorithm review<br>- Elimination of thrashing |

### Tuning Map (11/12)

#### Instruction count bottleneck

| High cost as seen from PA graph |                                                                                                 | High cost as seen from PA information | Condition | Tuning proposal                                                                                                                                   |

|---------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction<br>commit           | Four instructions<br>commit<br>Two or three<br>instructions commit<br>One instruction<br>commit |                                       |           | Improvement in the instruction<br>count bottleneck<br>- Facilitation of SIMD optimization<br>- Prefetch-related improvement<br>- Inline expansion |

### Tuning Map (12/12)

#### Other

| High cost as seen from<br>PA graph         | High cost as seen from<br>PA information | Condition                                 | Tuning proposal  |

|--------------------------------------------|------------------------------------------|-------------------------------------------|------------------|

| No instruction commit<br>for other reasons | _                                        | PA may have not been collected correctly. | PA re-collection |

# Tuning Technique List (1/2)

## FUĴĨTSU

## Major classifications

| Thread parallelization ratio<br>improvement                              | improvement of<br>thread parallelizatior<br>processing |                                                                       | Instruction scheduling<br>improvement                                                                                |                                          | instruction fetch                | Improvement in the<br>instruction count<br>bottleneck |

|--------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------|-------------------------------------------------------|

| NORECURRENCE specifier<br>(Facilitation of automatic<br>parallelization) |                                                        | displacement of an array                                              | Software pipelining                                                                                                  |                                          | body                             | Facilitation of SIMD<br>optimization                  |

| NOALIAS specifier<br>(Facilitation of automatic<br>parallelization)      | Parallelized<br>dimension change                       | Prefetch-related<br>improvement                                       | Unrolling                                                                                                            |                                          | (Expansion of the problem scale) | Prefetch-related<br>improvement                       |

| Peeling<br>(Facilitation of automatic<br>parallelization)                | change (Cyclic)                                        |                                                                       | Facilitation of SIMD optimization                                                                                    | Change of areas used                     | Elimination of thrashing         | Inline expansion                                      |

| OpenMP parallelization                                                   | Division method<br>change (Dynamic)                    | Loop blocking                                                         | IF statement removal                                                                                                 | Optimization using<br>large page options |                                  |                                                       |

|                                                                          | Parallelization<br>algorithm review                    | ,                                                                     | Masked SIMD                                                                                                          |                                          |                                  |                                                       |

|                                                                          |                                                        | Algorithm review<br>(Reducing the memory<br>access instruction ratio) | Outer unrolling                                                                                                      |                                          |                                  |                                                       |

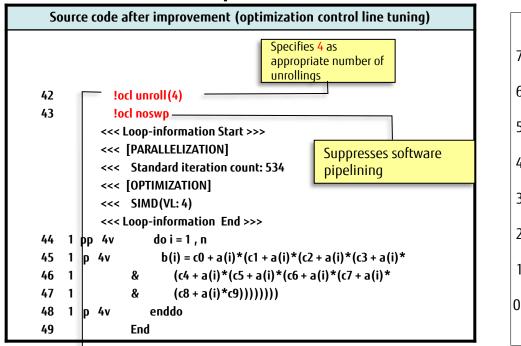

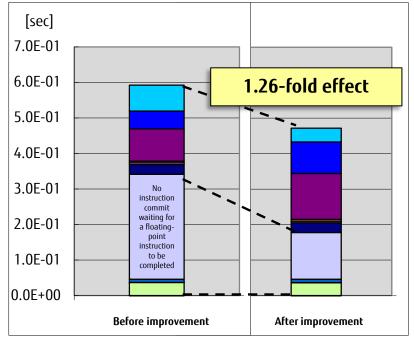

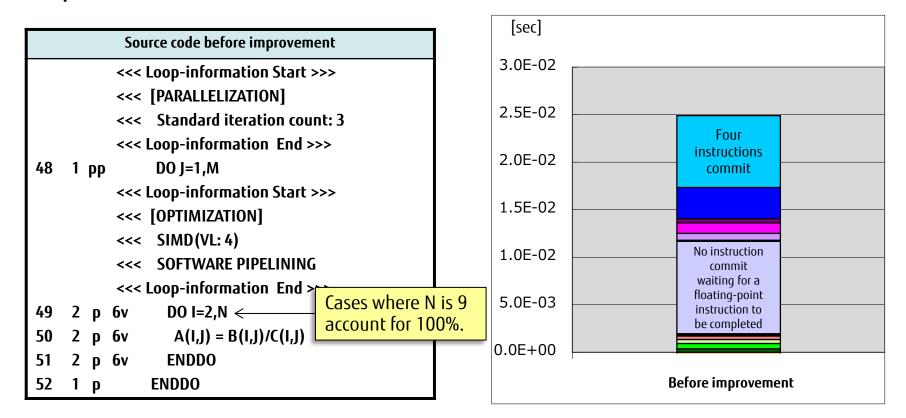

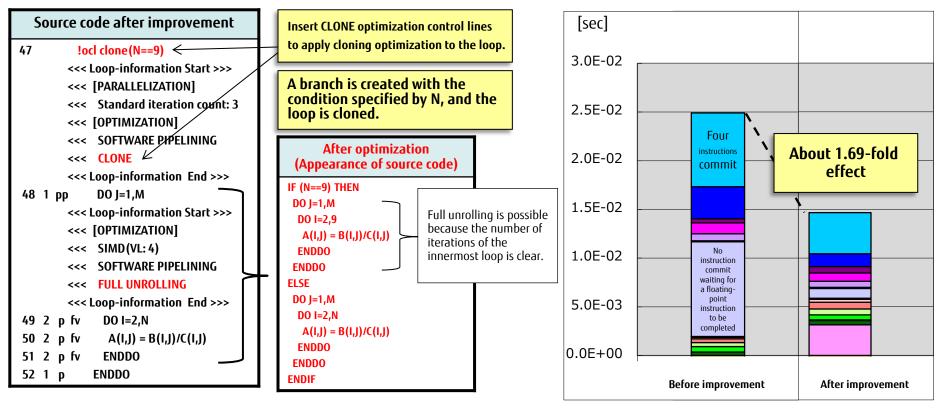

|                                                                          |                                                        | Array division                                                        | Suppression of software<br>pipelining & specification of the<br>number of unrollings (Loop with<br>a few iterations) |                                          |                                  |                                                       |

|                                                                          |                                                        | Loop fission                                                          | Rerolling                                                                                                            |                                          |                                  |                                                       |

|                                                                          |                                                        | Strip mining                                                          | Peeling                                                                                                              |                                          |                                  |                                                       |

|                                                                          |                                                        | Sector cache<br>Loop interchange                                      | NORECURRENCE specifier NOALIAS specifier                                                                             |                                          |                                  |                                                       |

|                                                                          |                                                        | Loop fusion                                                           |                                                                                                                      |                                          |                                  |                                                       |

|                                                                          |                                                        | Array merging                                                         |                                                                                                                      |                                          |                                  |                                                       |

\* The colored items represent medium classifications. If applicable, go to the next page.

# Tuning Technique List (2/2)

## Medium classifications

| Prefetch-related improvement        | Facilitation of SIMD optimization                                   | Elimination of thrashing                | Reduction in the loop body         |

|-------------------------------------|---------------------------------------------------------------------|-----------------------------------------|------------------------------------|

| Addition of prefetching             | Changing arrays to simple variables                                 | Padding                                 | Suppression of software pipelining |

| Deletion of unnecessary prefetching | Loop unswitching                                                    | Dimensional<br>displacement of an array | Suppression of unrolling           |

| Prefetching toward the outer loop   | IF statement removal                                                | Array merging                           | Suppression of loop fusion         |

| Indirect access prefetching         | Rerolling                                                           | Reduction in the loop<br>body           | Loop fission                       |

|                                     | Inline expansion                                                    |                                         |                                    |

|                                     | Loop fission (separating dependent<br>accesses)                     |                                         |                                    |

|                                     | Loop fission (loop extraction) for a part<br>with a high true ratio |                                         |                                    |

|                                     | Cloning                                                             |                                         |                                    |

|                                     | NORECURRENCE specifier                                              |                                         |                                    |

|                                     | NOALIAS specifier                                                   |                                         |                                    |

FUITSU

# Scalar Tuning

- Improvement in Data Access Wait (Improvement in Thrashing)

- Improvement in Data Access Wait (Increase in Data Locality)

- Improvement in Data Access Wait (Latency Concealment)

- Improvement in Data Access Wait (Reduced Amount of Access)

- Improvement in Operation Wait (Instruction Scheduling Improvement)

## Improvement in Data Access Wait (Improvement in Thrashing)

Improvement in Cache Thrashing

Improvement in TLB Thrashing

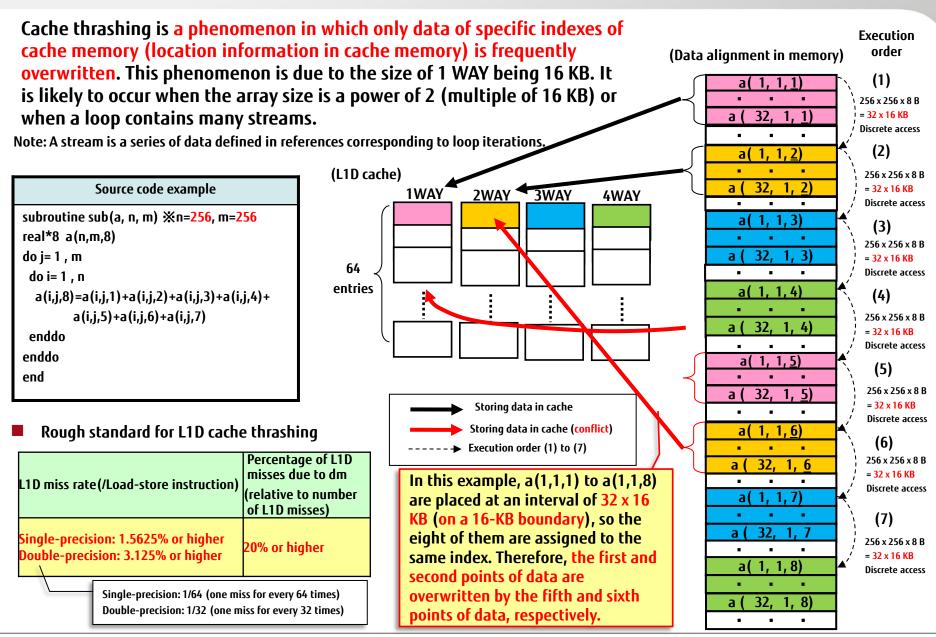

# Improvement in Cache Thrashing

- What Is Cache Thrashing?

- Tuning Approach to Cache Thrashing (Basics)

- Tuning Approach to Cache Thrashing (Application)

# What Is Cache Thrashing?

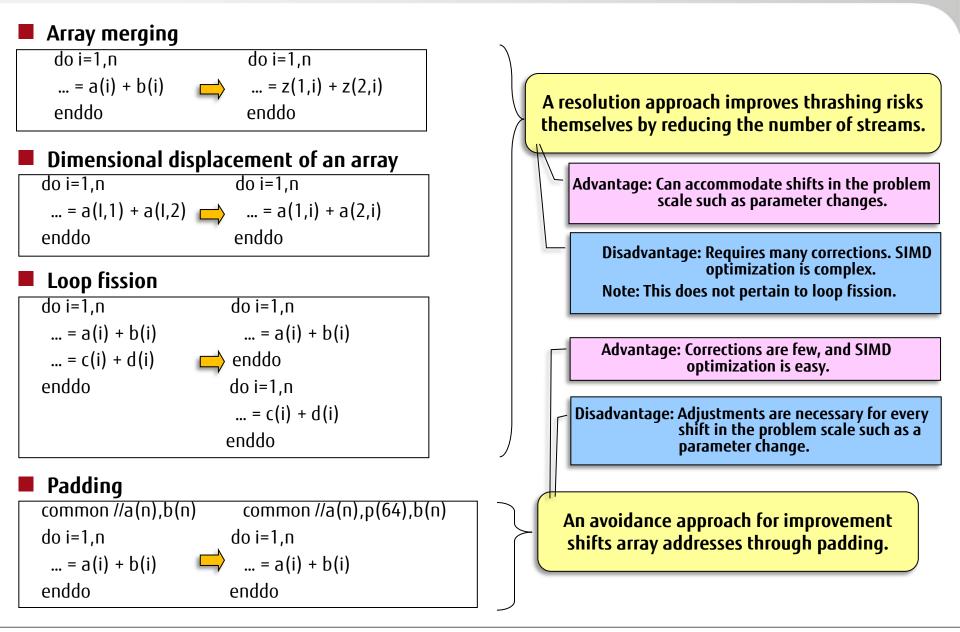

# Tuning Approach to Cache Thrashing (Basics)

- Tuning Approach (Basics)

- Array Merging

- Dimensional Displacement of an Array

- Loop Fission

- Padding

Chapter 8 Tuning Approach to Cache Thrashing (Basics)

# Tuning Approach (Basics)

Chapter 8 Tuning Approach to Cache Thrashing (Basics)

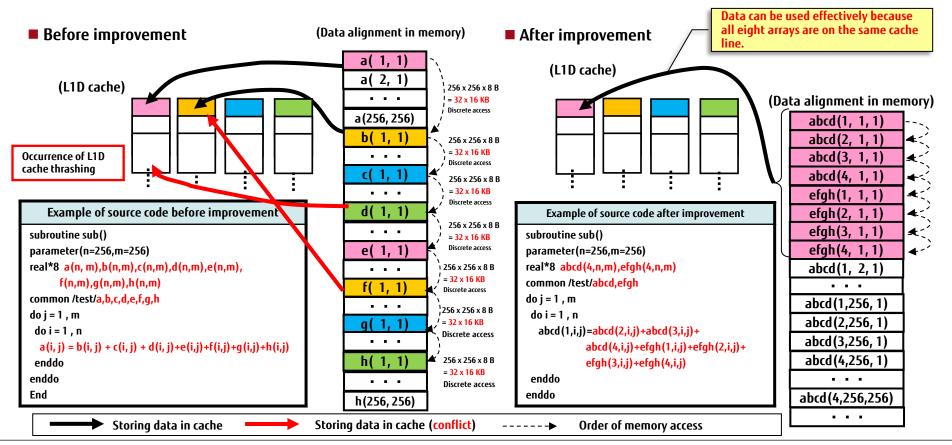

# Array Merging

- What Is Array Merging?

- Array Merging (Before Improvement)

- Effects of Array Merging (Source Tuning)

- Array Merging (in C Language) (Before Improvement)

- Effects of Array Merging (in C Language) (Source Tuning)

- Effects of Array Merging (Compiler Options Tuning)

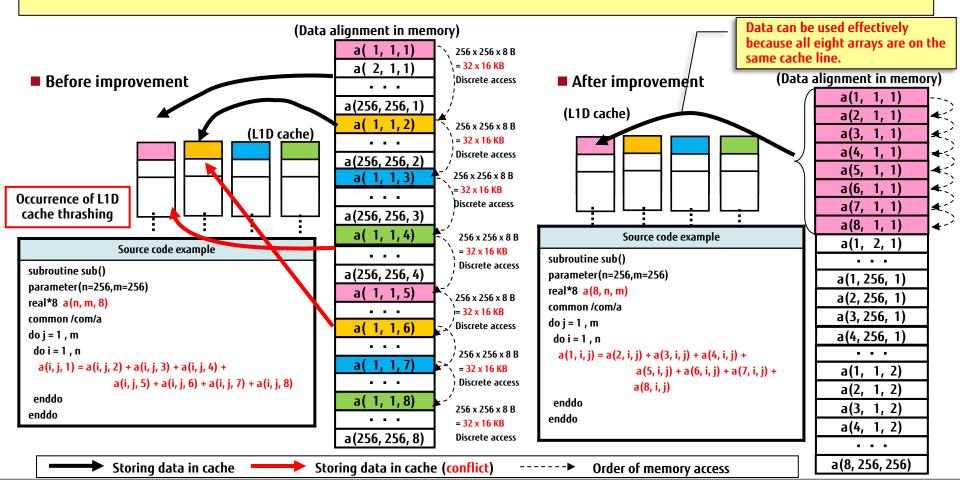

# What Is Array Merging?

## Array merging is tuning that merges multiple arrays into one array.

### Use conditions

Each array to be merged has the same number of elements.

#### Purpose

- The purpose is to reduce the number of streams.

- Adverse effect

- Load and store instructions become stride or indirect instructions.

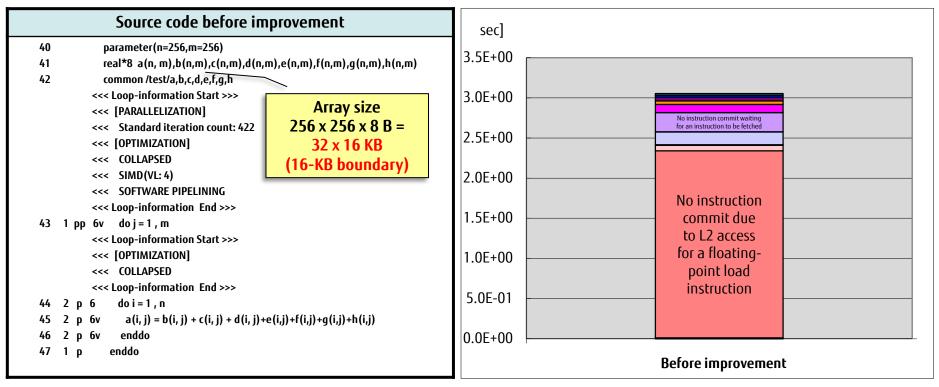

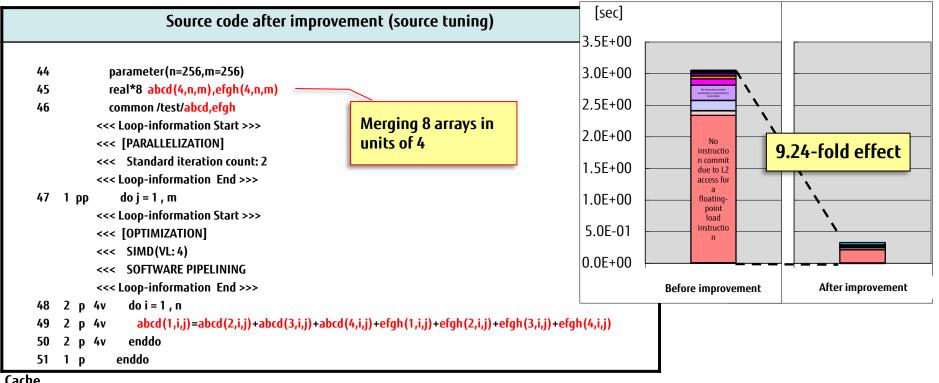

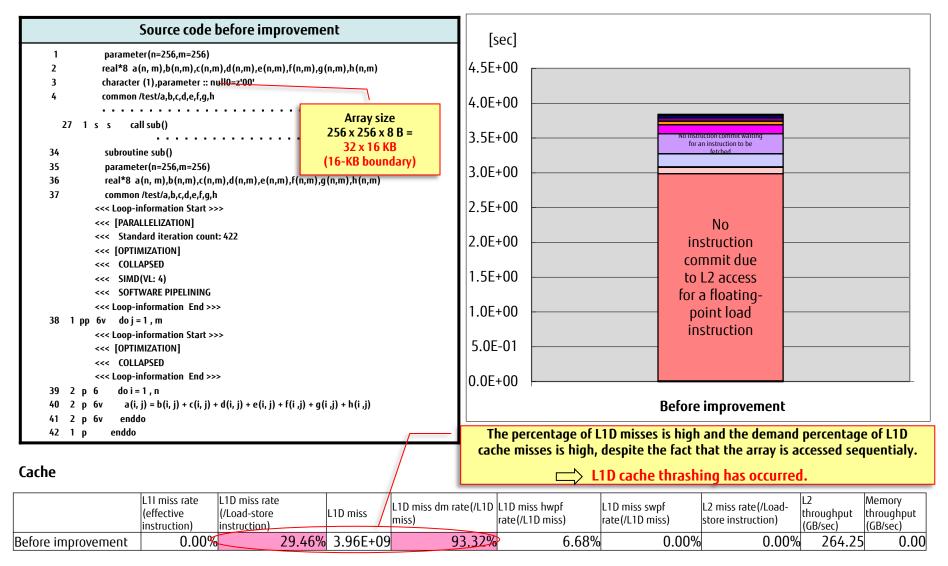

# Array Merging (Before Improvement)

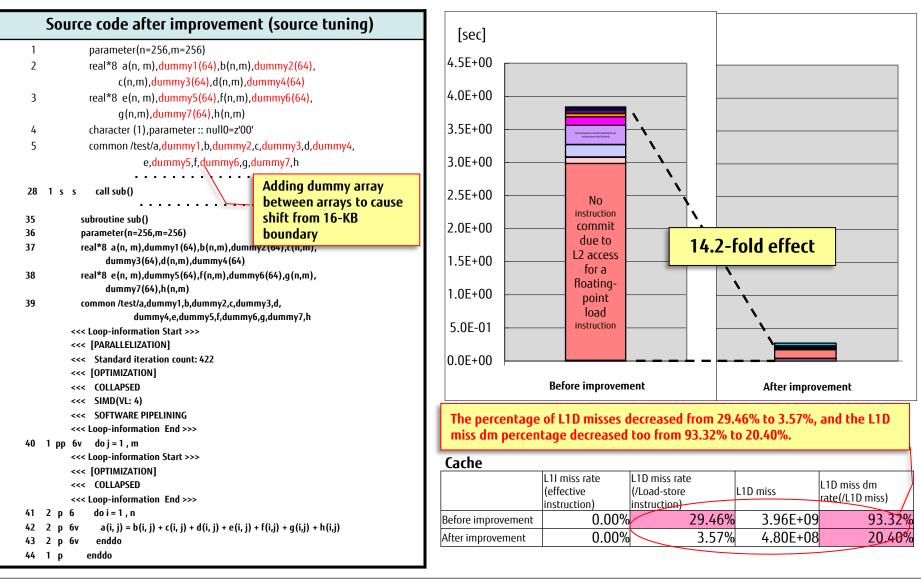

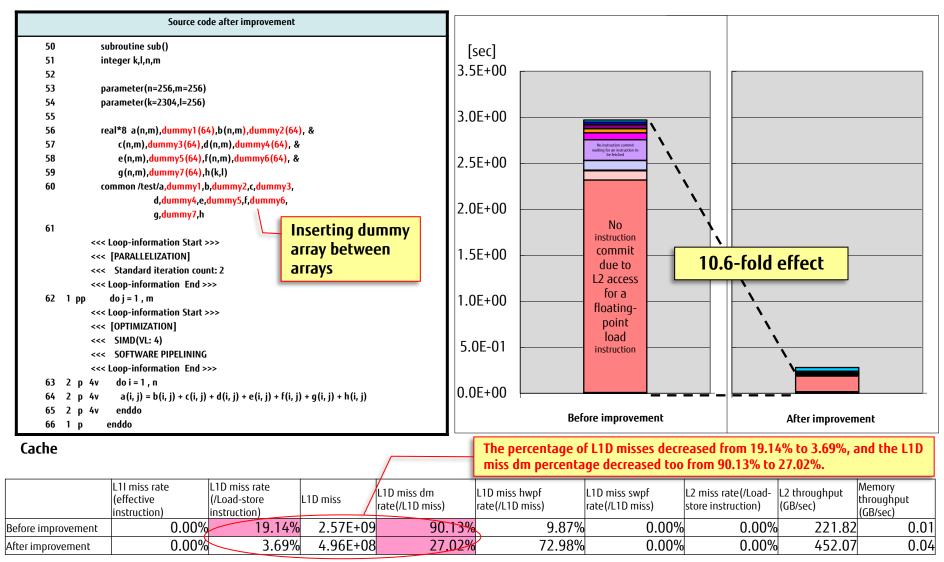

L1D cache thrashing occurs because each array is located on a 16-KB boundary. Consequently, the following is a frequent event: No instruction commit due to L2 access for a floating-point load instruction.

#### Cache

|                       | L11 miss rate(/Effective<br>instruction) | L1D miss rate<br>(/Load-store<br>instruction) | III) micc |        | L1D miss hwpf<br>rate(/L1D miss) | L1D miss swpf<br>rate(/L1D miss) | 1     | Memory throughput<br>(GB/sec) | L2 throughput<br>(GB/sec) |

|-----------------------|------------------------------------------|-----------------------------------------------|-----------|--------|----------------------------------|----------------------------------|-------|-------------------------------|---------------------------|

| Before<br>improvement | 0.00%                                    | 23.21%                                        | 3.12E+09  | 91.66% | 8.34%                            | 0.00%                            | 0.00% | 0.00                          | 261.73                    |

Chapter 8 Array Merging

Copyright 2016 FUJITSU LIMITED

The percentage of L1D misses is high and the L1 miss dm percentage is high,

despite the fact that the array is accessed sequentialy.

$\equiv$  L1D cache thrashing has occurred.

# Effects of Array Merging (Source Tuning)

Array merging reduced the number of streams from eight to two, so L1D cache thrashing was avoided. This results in improvement of the following event: No instruction commit due to L2 access for a floating-point load instruction.

#### Cache

|                       | L1I miss<br>rate(/Effective<br>instruction) | L1D miss rate<br>(/Load-store<br>instruction) | L1D miss | L1D miss dm<br>rate(/L1D miss) | L1D miss hwpf<br>rate(/L1D miss) | L1D miss swpf<br>rate(/L1D miss) | L2 miss rate(/Load-<br>store instruction) | Memory<br>throughput<br>(GB/sec) | L2 throughput (GB/sec) |

|-----------------------|---------------------------------------------|-----------------------------------------------|----------|--------------------------------|----------------------------------|----------------------------------|-------------------------------------------|----------------------------------|------------------------|

| Before<br>improvement | 0.00%                                       | 23.21%                                        | 3.12E+09 | 91.66%                         | 8.34%                            | 0.00%                            | 0.00%                                     | 0.00                             | 261.73                 |

| After<br>improvement  | 0.00%                                       | 3.19%                                         | 4.29E+08 | 25.52%                         | 74.48%                           | 0.00%                            | 0.00%                                     | 0.01                             | 335.65                 |

The percentage of L1D cache misses decreased from 23.21% to 3.19%, and the L1D miss dm percentage decreased too from 91.66% to 25.52%.

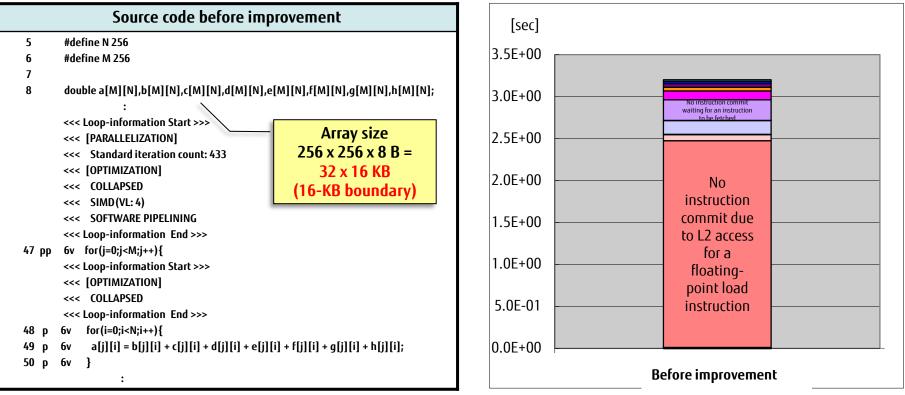

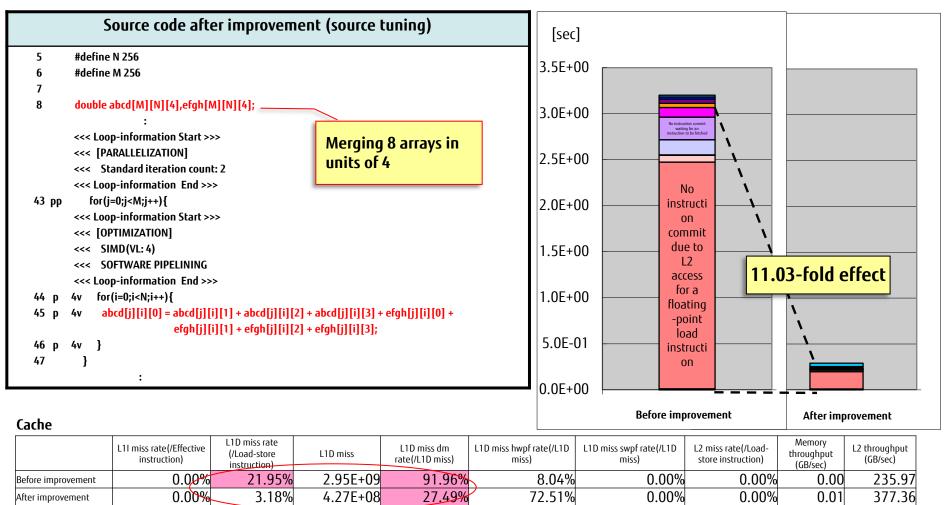

## Array Merging (in C Language) (Before Improvement) Fujirsu

L1D cache thrashing occurs because each array is located on a 16-KB boundary. Consequently, the following is a frequent event: No instruction commit due to L2 access for a floating-point load instruction.

#### Cache

|                       | L1I miss rate(/Effective instruction) | L1D miss rate<br>(/Load-store<br>inst <u>ruction)</u> | L1D miss | L1D miss dm<br>rate(/L1D miss) | L1D miss hwpf<br>rate(/L1D miss) |       |       | Memory throughput<br>(GB/sec) | L2 throughput<br>(GB/sec) |

|-----------------------|---------------------------------------|-------------------------------------------------------|----------|--------------------------------|----------------------------------|-------|-------|-------------------------------|---------------------------|

| Before<br>improvement | 0.00%                                 | 21.95%                                                | 2.95E+09 | 91.96%                         | 8.04%                            | 0.00% | 0.00% | 0.00                          | 235.97                    |

|                       |                                       |                                                       |          |                                |                                  |       |       |                               |                           |

The percentage of L1D misses is high and the L1 miss dm percentage is high, despite the fact that the array is accessed sequentialy.

## Effects of Array Merging (in C Language) (Source Tuning) Fujitsu

Array merging reduced the number of streams from eight to two, so L1D cache thrashing was avoided. This results in improvement of the following event: No instruction commit due to L2 access for a floating-point load instruction.

The percentage of L1D cache misses decreased from 21.95% to 3.18%, and the L1D miss dm percentage decreased too from 91.96% to 27.49%.

# You can achieve effects similar to source tuning by specifying the following compiler options.

| Compiler options                         | Description of function                                                                                                                                                                   |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -Karray_merge_common<br>[= <i>name</i> ] | Gives an instruction to merge multiple arrays in a common block. You can specify a common block name for name. If name is omitted, the arrays in all the named common blocks are targets. |

| -Karray_merge_local                      | Gives an instruction to merge multiple local arrays.<br>-Karray_merge_local_size=1000000 is also valid at the same time.                                                                  |

| -Karray_merge                            | This option is equivalent to specifying the -Karray_merge_local and -Karray_merge_common options.                                                                                         |

## Use example (source code before improvement)

\$ frtpx -Kfast,parallel sample.f90 -Karray\_merge\_common

## Notes

- •Options must be specified for all source code that uses the target arrays.

- •The effects of array merging vary depending on the program.

- •Incorrect use may result in different computational results.

- •These options cannot be used with debug options (-g and -Haesux).

# FUJITSU

# Dimensional Displacement of an Array

- What Is Dimensional Displacement of an Array?

- Dimensional Displacement of an Array (Before Improvement)

- Effects of Dimensional Displacement of an Array (Source Tuning)

- Dimensional Displacement of an Array (in C Language) (Before Improvement)

- Effects of Dimensional Displacement of an Array (in C Language) (Source Tuning)

- Effects of Dimensional Displacement of an Array (Compiler Options Tuning)

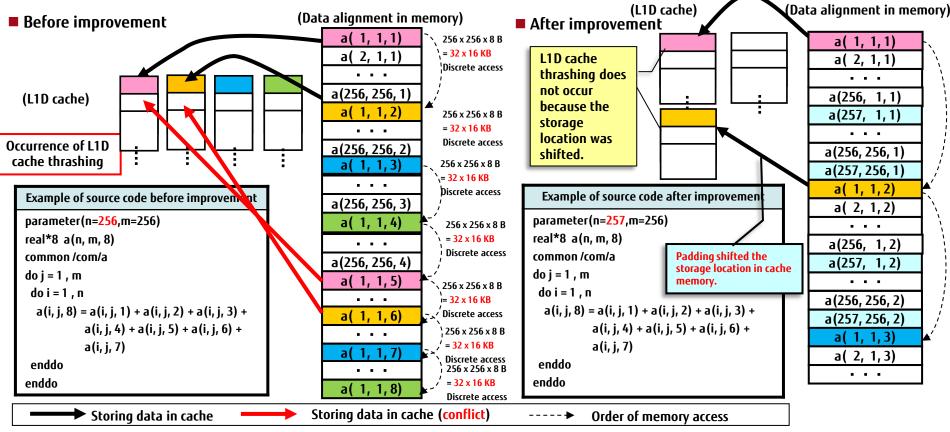

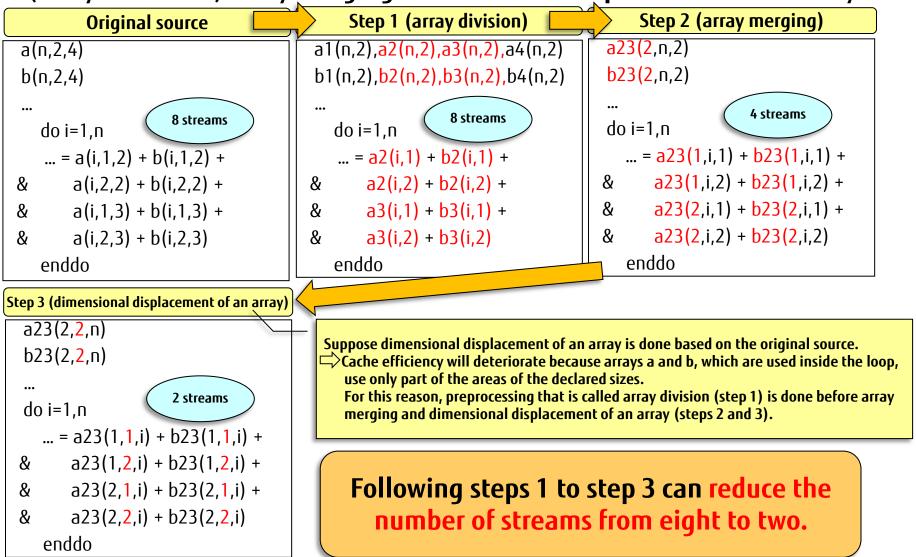

## What Is Dimensional Displacement of an Array?

Dimensional displacement of an array is a tuning method where multiple streams of the same array become one stream.

### Use conditions

Multiple streams exist in the same array. \* a(1,1,1) to a(1,1,8) are shown as multiple streams.

### Purpose

- The purpose is to reduce the number of streams.

- Adverse effect

- SIMD optimization of load and store instructions is more difficult.

Chapter 8 Dimensional Displacement of an Array

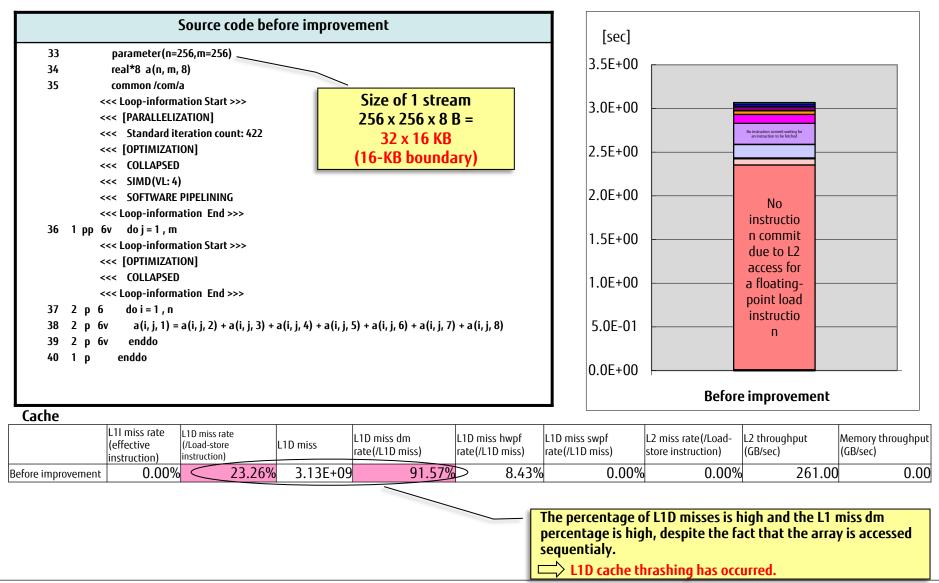

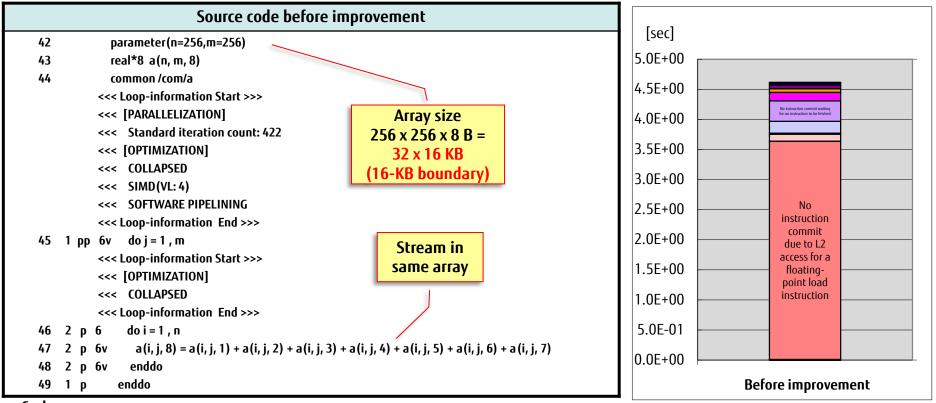

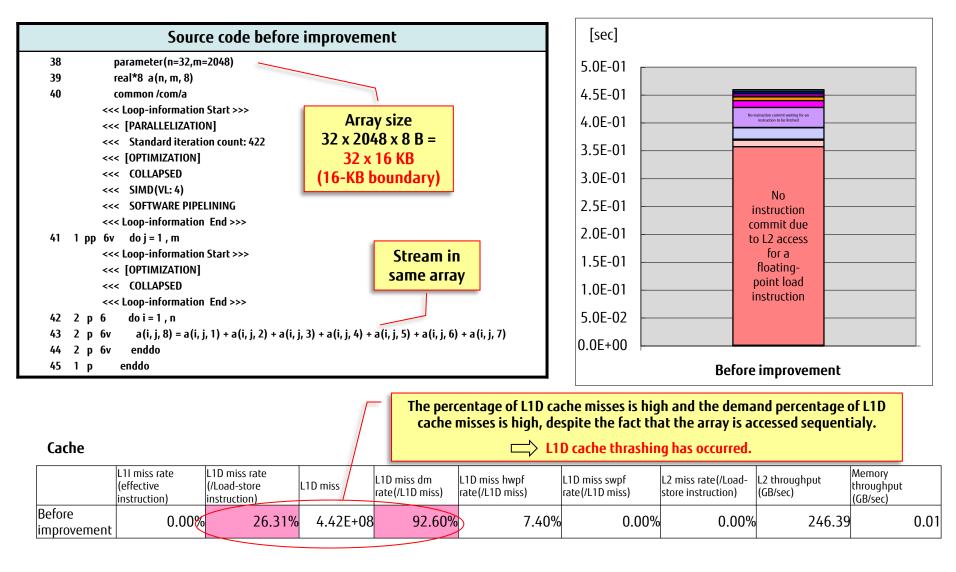

## Dimensional Displacement of an Array (Before Improvement) Fujitsu

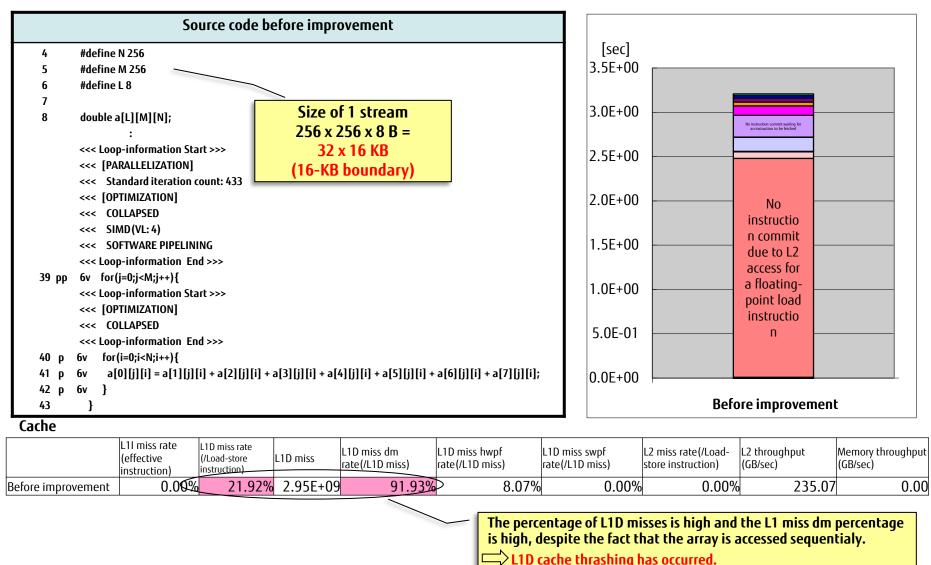

L1D cache thrashing occurs because each stream of array a is located on a 16-KB boundary. Consequently, the following is a frequent event: No instruction commit due to L2 access for a floating-point load instruction.

53

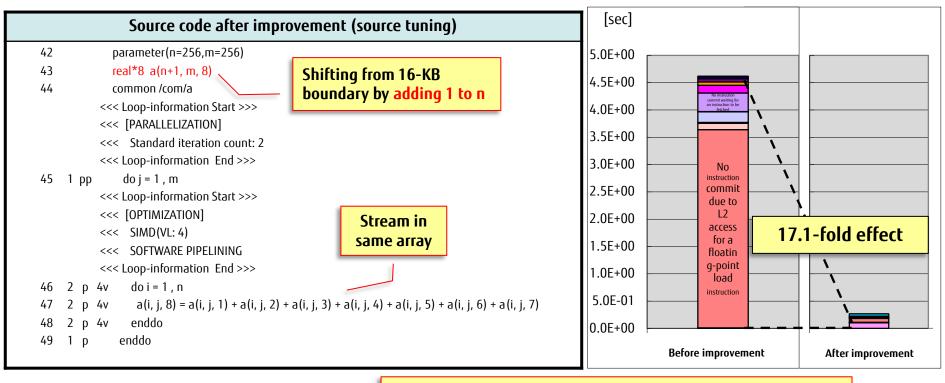

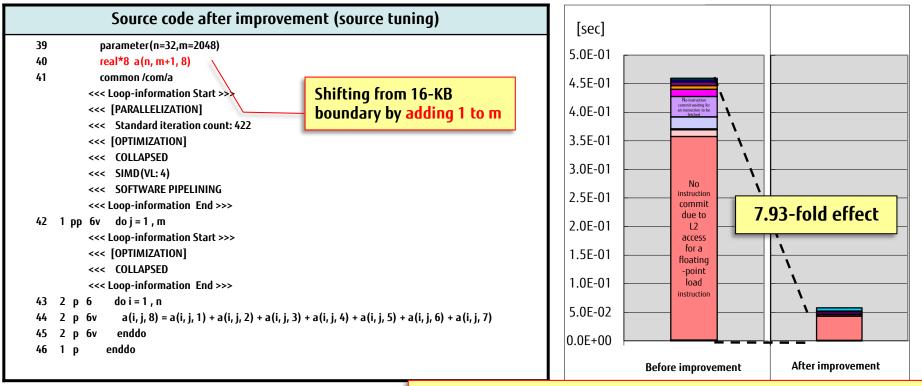

## Effects of Dimensional Displacement of an Array (Source Tuning)

Dimensional displacement of an array reduced the number of streams from eight to one, so L1D cache thrashing was avoided. This results in improvement of the following event: No instruction commit due to L2 access for a floating-point load instruction.

#### Cache

| L11 miss<br>(effective<br>instructio | (/L   | D miss rate<br>Load-store I<br>struction) | III) micc I |        | L1D miss hwpf<br>rate(/L1D miss) | L1D miss swpf<br>rate(/L1D miss) | ,     | 51     | Memory throughput<br>(GB/sec) |

|--------------------------------------|-------|-------------------------------------------|-------------|--------|----------------------------------|----------------------------------|-------|--------|-------------------------------|

| Before improvement                   | ).00% | 23.26%                                    | 3.13E+09    | 91.57% | 8.43%                            | 0.00%                            | 0.00% | 261.00 | 0.00                          |

| After improvement                    | ).00% | 3.16%                                     | 4.27E+08    | 20.03% | 79.97%                           | 0.00%                            | 0.00% | 207.01 | 0.00                          |

# The percentage of L1D misses decreased from 23.26% to 3.16%, and the L1D miss dm percentage decreased too from 91.57% to 20.03%.

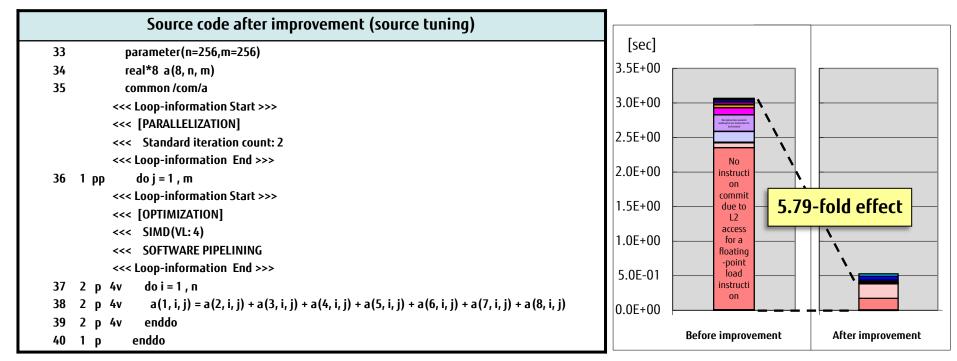

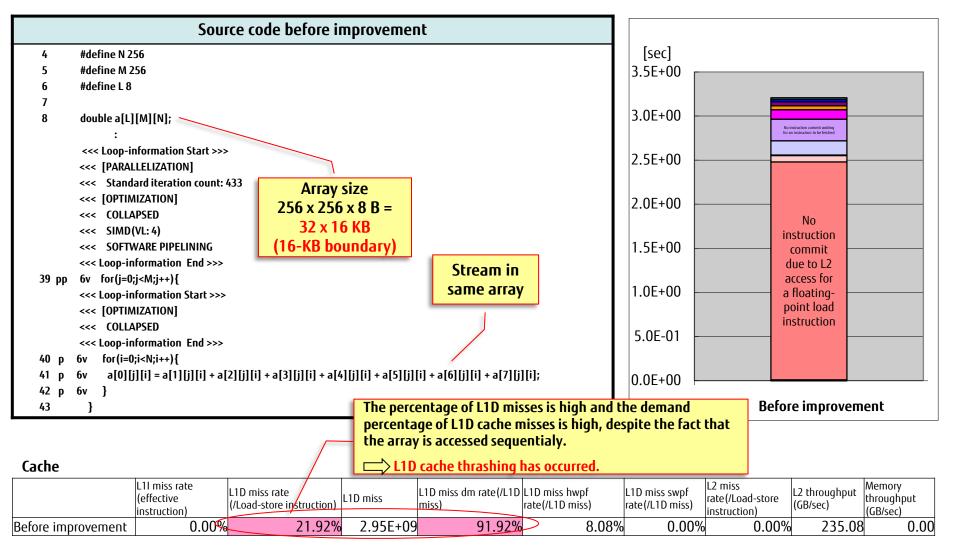

### Dimensional Displacement of an Array (in C Language) (Before Improvement)

L1D cache thrashing occurs because each stream of array a is located on a 16-KB boundary. Consequently, the following is a frequent event: No instruction commit due to L2 access for a floating-point load instruction.

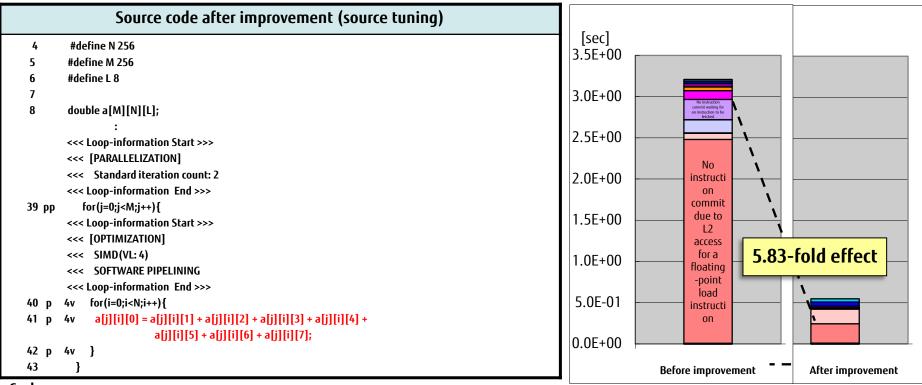

### Effects of Dimensional Displacement of an Array (in C Language) (Source Tuning)

Dimensional displacement of an array reduced the number of streams from eight to one, so L1D cache thrashing was avoided. This results in improvement of the following event: No instruction commit due to L2 access for a floating-point load instruction.

#### Cache

|                    | L1I miss rate<br>(effective<br>instruction) | L1D miss rate<br>(/Load-store<br>instruction) | L1D miss | L1D miss dm<br>rate(/L1D miss) | L1D miss hwpf rate(/L1D<br>miss) |       | L2 miss rate(/Load-<br>store instruction) | L2 throughput | Memory<br>throughput<br>(GB/sec) |

|--------------------|---------------------------------------------|-----------------------------------------------|----------|--------------------------------|----------------------------------|-------|-------------------------------------------|---------------|----------------------------------|

| Before improvement | 0.00%                                       | 21.92%                                        | 2.95E+09 | 91.93%                         | 8.07%                            | 0.00% | 0.00%                                     | 235.07        | 0.00                             |

| After improvement  | 0.00%                                       | 3.16%                                         | 4.27E+08 | 22.84%                         | 77.16%                           | 0.00% | 0.00%                                     | 199.05        | 0.00                             |

# The percentage of L1D misses decreased from 21.92% to 3.16%, and the L1D miss dm percentage decreased too from 91.93% to 22.84%.

FUITSU

### You can achieve effects similar to source tuning by specifying the following compiler options.

| Compiler options                                       | Description of function                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| -Karray_subscript                                      | Gives an instruction for dimensional displacement of allocatable arrays with 4 or more dimensions and arrays with 4 or more dimensions containing 10 or fewer elements in the final dimension and 100 or more elements in the other dimensions.                                                                     |  |  |  |  |  |  |

|                                                        | -Karray_subscript_element=100,-Karray_subscript_elementlast=10,                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                                                        | and -Karray_subscript_rank=4 are also valid at the same time.                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| -Karray_subscript_element=N<br>(2≦N≦2,147,483,647)     | Gives an instruction that the number of elements in a dimension other than the final<br>dimension in an array subject to dimensional displacement be N or greater. This option has<br>meaning in cases where the -Karray_subscript option is valid. However, the option has no<br>meaning for an allocatable array. |  |  |  |  |  |  |

| -Karray_subscript_elementlast=N<br>(2≦N≦2,147,483,647) | Gives an instruction that the number of elements in the final dimension of an array subject to dimensional displacement be N or less. This option has meaning in cases where the -Karray_subscript option is valid. However, the option has no meaning for an allocatable array.                                    |  |  |  |  |  |  |

| -Karray_subscript_rank=N<br>(2≦N≦30)                   | Gives an instruction that the number of dimensions of an array subject to dimensional displacement be N or greater. This option has meaning in cases where the -Karray_subscript option is valid.                                                                                                                   |  |  |  |  |  |  |

| Use example (source code before improvement)           |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

### \$ frtpx -Kfast,parallel sample.f90

-Karray\_subscript,array\_subscript\_rank=2,array\_subscript\_element=2

### Notes

- •Options must be specified for all source code that uses the target arrays.

- •The effects of displacement vary depending on the program.

- •Incorrect use may result in different computational results.

# Loop Fission

- Loop Fission (Before Improvement)

- Effects of Loop Fission (Source Tuning)

- Loop Fission (in C Language) (Before Improvement)

- Effects of Loop Fission (in C Language) (Source Tuning)

- Effects of Loop Fission (Optimization Control Line Tuning)

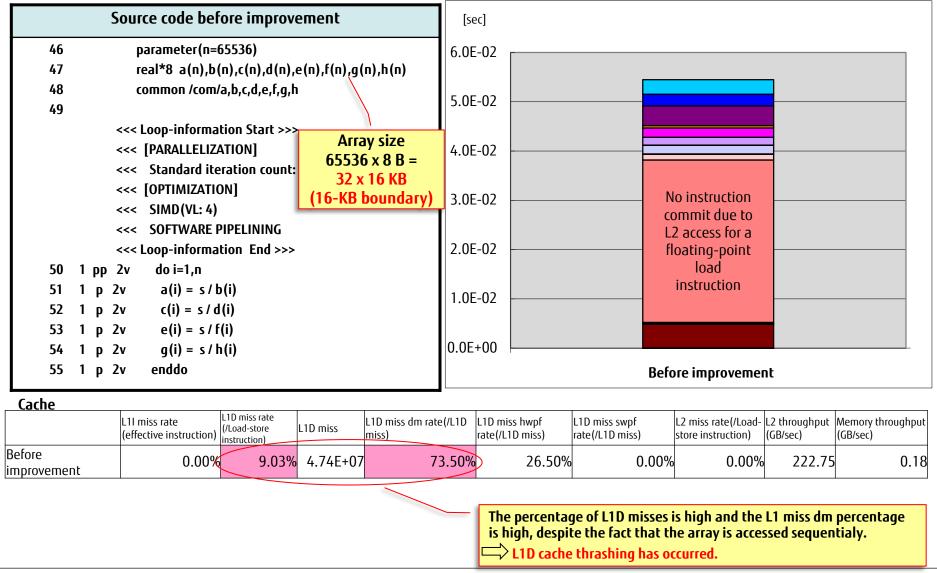

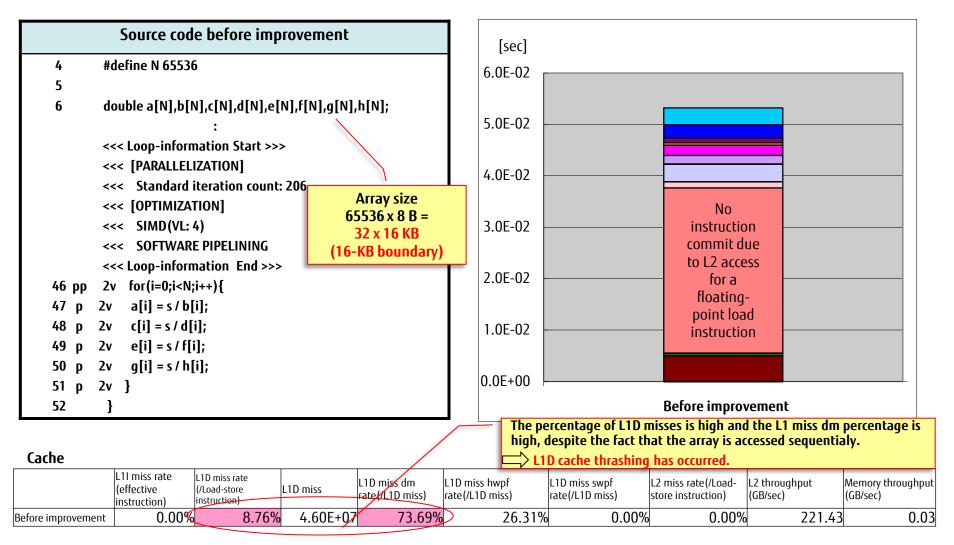

## Loop Fission (Before Improvement)

L1D cache thrashing occurs because each array is located on a 16-KB boundary. Consequently, the following is a frequent event: No instruction commit due to L2 access for a floating-point load instruction.

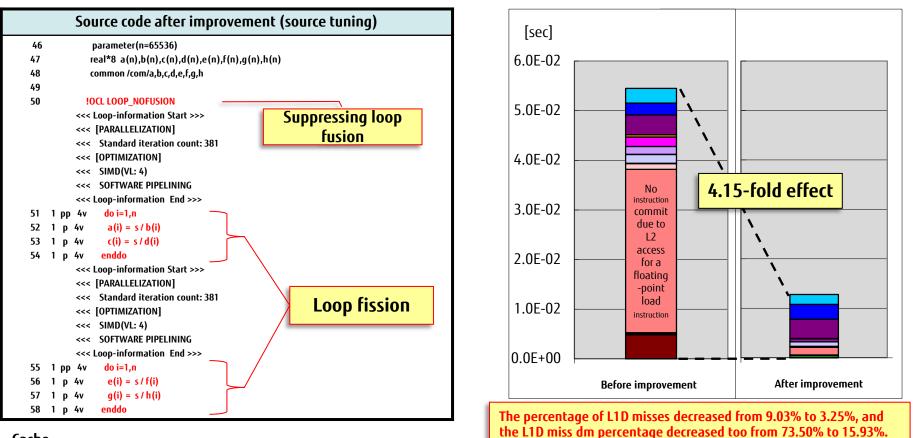

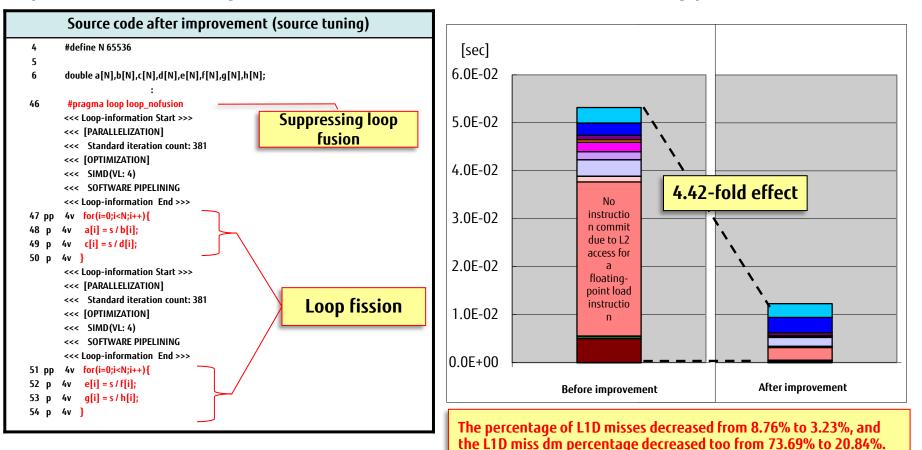

# Effects of Loop Fission (Source Tuning)

Loop fission reduced the number of streams from eight to four, so L1D cache thrashing was avoided. This results in improvement of the following event: No instruction commit due to L2 access for a floating-point load instruction.

#### Cache

| Cacine             |            |                                               |            |                                |                       |        |                                  |                                       |        |                               |

|--------------------|------------|-----------------------------------------------|------------|--------------------------------|-----------------------|--------|----------------------------------|---------------------------------------|--------|-------------------------------|

|                    | (effective | L1D miss rate<br>(/Load-store<br>instruction) | L1D miss   | L1D miss dm<br>rate(/L1D miss) | L1D miss<br>rate(/L1[ |        | L1D miss swpf rate(/L1D<br>miss) | L2 miss rate(/Load-store instruction) |        | Memory throughput<br>(GB/sec) |

| Before improvement | 0.00%      | 9.03%                                         | 4.74E+07   | 73.50%                         |                       | 26.50% | 0.00%                            | 0.00%                                 | 222.75 | 0.18                          |

| After improvement  | 0.00%      | 3.25%                                         | 5 1.71E+07 | 15.93%                         |                       | 84.07% | 0.00%                            | 0.00%                                 | 341.98 | 0.70                          |

## Loop Fission (in C Language) (Before Improvement) Fujitsu

L1D cache thrashing occurs because each array is located on a 16-KB boundary. Consequently, the following is a frequent event: No instruction commit due to L2 access for a floating-point load instruction.

## Effects of Loop Fission (in C Language) (Source Tuning) Fujitsu

Loop fission reduced the number of streams from eight to four, so L1D cache thrashing was avoided. This results in improvement of the following event: No instruction commit due to L2 access for a floating-point load instruction.

#### Cache

|                    | L11 miss rate<br>(effective<br>instruction) | L1D miss rate<br>(/Load-store<br>instruction) |       | L1D miss I |        | L1D m <del>iss hwpf</del> rate(/L1D<br>miss) |       | ,     |        | Memory throughput<br>(GB/sec) |

|--------------------|---------------------------------------------|-----------------------------------------------|-------|------------|--------|----------------------------------------------|-------|-------|--------|-------------------------------|

| Before improvement | 0.00%                                       | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~       | 8.76% | 4.60E+07   | 73.69% | 26.31%                                       | 0.00% | 0.00% | 221.43 | 0.03                          |

| After improvement  | 0.00%                                       |                                               | 3.23% | 1.70E+07   | 20.84% | 79.16%                                       | 0.00% | 0.00% | 353.87 | 0.02                          |

## Effects of Loop Fission (Optimization Control Line Tuning)

### You can achieve effects similar to source tuning by specifying the following optimization control line.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                      | Optimiz         | ation control l | ine that can b    | e specified                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-------------------|------------------------------------------|

| Optimization control specifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Meaning                                                                                                                                                                                              | Program<br>unit | DO loop<br>unit | Statement<br>unit | Array<br>assignment<br>statement<br>unit |

| !OCL FISSION_POINT[( <i>n</i> 1)]<br>(where <i>n1</i> is decimal<br>number from 1 to 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Gives an instruction for loop fission at the specified point<br>inside a loop. The loop fission divides multiple loops that<br>have loops nested to n1 levels (counting from the innermost<br>loop). | No              | No              | Yes               | No                                       |

| Source code after im                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | provement (optimization control line tuning)                                                                                                                                                         |                 |                 |                   |                                          |

| 46       parameter (n=655         47       real*8 a (n),b(n),         48       common /com/a,b         49          49          49          49          49          49          49          49          49          49          49          49          49          49          49          49          49          49          49          49          49          49          49          <<       Standard iterat         <<       SPLIT         <<<       SOFTWARE PIPI         <<<       SOFTWARE PIPI         <<<       s/d(i)         52       1       p         55       1       p         56       1       p         sin d       g(i) = s/h(i)      < | <pre>(n),d(n),e(n),f(n),g(n),h(n) ),c,d,e,f,g,h n Start &gt;&gt;&gt; ON] ion count: 381 ELINING n End &gt;&gt;&gt; (1)</pre>                                                                         |                 |                 |                   |                                          |

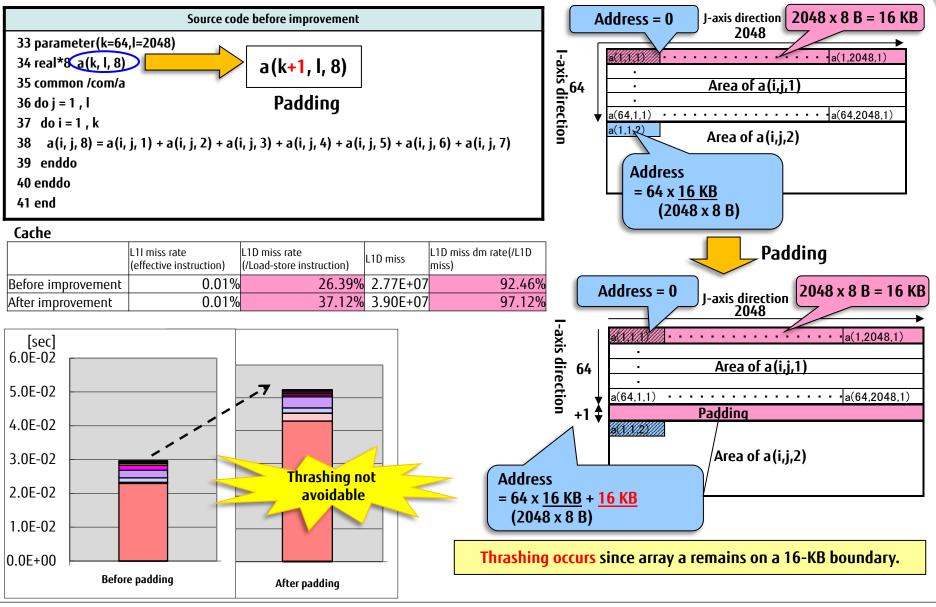

# Padding

- What Is Padding?

- Padding That Increases the Number of Array Elements in the First Dimension

- Padding That Increases the Number of Array Elements in the Second Dimension

- Padding Using a Dummy Array

- Padding Using a Dummy Array (for Arrays of Different Sizes)

# What Is Padding?

### Padding inserts a dummy area between arrays or inside an array.

### Use conditions

#### Purpose

Multiple streams exist in the same array. Alternatively,

Multiple arrays exist.

The purpose is to create a temporary area to shift addresses.

### Adverse effect

The amount of padding must be changed every time that the problem scale changes.

#### Example where multiple streams exist in the same array

# Padding That Increases the Number of Array Elements in the First Dimension

- Padding That Increases the Number of Array Elements in the First Dimension (Before Improvement)

- Effects of Padding That Increases the Number of Array Elements in the First Dimension (Source Tuning)

- Padding That Increases the Number of Array Elements in the First Dimension (in C Language) (Before Improvement)

- Effects of Padding That Increases the Number of Array Elements in the First Dimension (in C Language) (Source Tuning)

- Effects of Padding That Increases the Number of Array Elements in the First Dimension (Compiler Options Tuning)

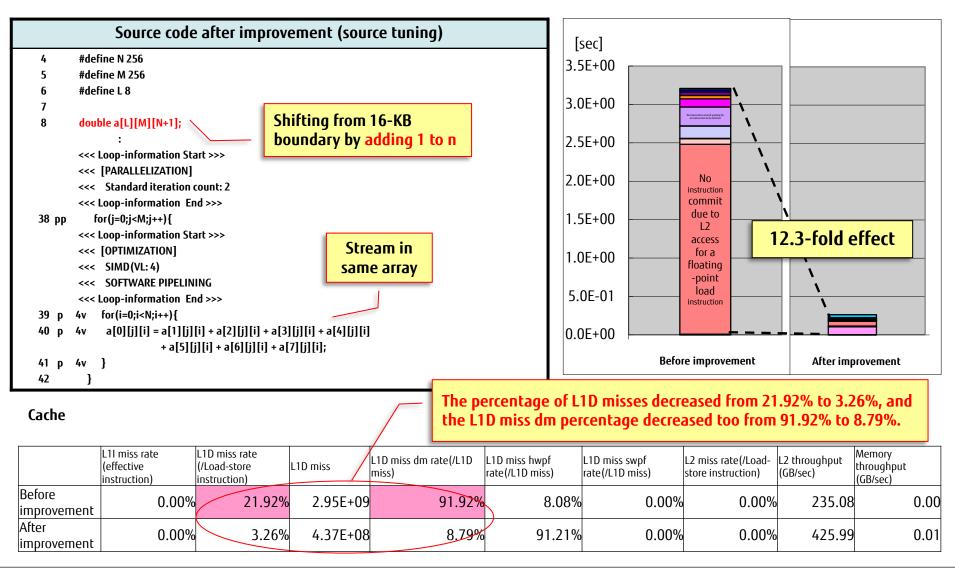

L1D cache thrashing occurs because each stream of array a is located on a 16-KB boundary. Consequently, the following is a frequent event: No instruction commit due to L2 access for a floating-point load instruction.

#### Cache

|                    | (effective instruction) | L1D miss rate<br>(/Load-store<br>instru <u>ction)</u> | L1D miss |        |       | L1D miss swpf<br>rate(/L1D miss) | L2 miss rate(/Load-<br>store instruction) | L2 throughput | Memory<br>throughput<br>(GB/sec) |

|--------------------|-------------------------|-------------------------------------------------------|----------|--------|-------|----------------------------------|-------------------------------------------|---------------|----------------------------------|

| Before improvement | 0.00%                   | 33.19%                                                | 4.47E+09 | 95.12% | 4.88% | 0.00%                            | 0.00%                                     | 247.59        | 0.00                             |

The percentage of L1D cache misses is high and the demand percentage of L1D cache misses is high, despite the fact that the array is accessed sequentialy.

## L1D cache thrashing was avoided because of padding (+1) of the first dimension of each stream of array a. This results in improvement of the following event: No instruction commit due to L2 access for a floating-point load instruction.

The percentage of L1D misses decreased from 33.19% to 3.27%, and the L1D miss dm percentage decreased too from 95.12% to 9.46%.

|                       |       | L1D miss rate<br>(/Load-store instruction)- | L1D miss | II III miss am ratel/I III missi |        |       | L2 miss rate(/Load-<br>store instruction) |        | Memory throughput<br>(GB/sec) |

|-----------------------|-------|---------------------------------------------|----------|----------------------------------|--------|-------|-------------------------------------------|--------|-------------------------------|

| Before<br>improvement | 0.00% | 33.19%                                      | 4.47E+09 | 95.12%                           | 4.88%  | 0.00% | 0.00%                                     | 247.59 | 0.00                          |

| After<br>improvement  | 0.00% | 3.27%                                       | 4.39E+08 | 9.46%                            | 90.54% | 0.00% | 0.00%                                     | 421.35 | 0.01                          |

Cache

# Padding That Increases the Number of Array Elements in the First Dimension (in C Language) (Before Improvement)

L1D cache thrashing occurs because each stream of array a is located on a 16-KB boundary. Consequently, the following is a frequent event: No instruction commit due to L2 access for a floating-point load instruction.

# Effects of Padding That Increases the Number of Array Elements in the First Dimension (in C Language) (Source Tuning)

L1D cache thrashing was avoided because of padding (+1) of the first dimension of each stream of array a. This results in improvement of the following event: No instruction commit due to L2 access for a floating-point load instruction.

Chapter 8 Padding That Increases the Number of Array Elements in the First Dimension

# You can achieve effects similar to source tuning by specifying the following compiler options.

| Compiler options                            | Description of function                                                                                                                                                                                                                                                                       |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -Karraypad_const[=N]<br>(1≦N≦2,147,483,647) | Pads <i>N</i> elements of an array whose first dimension is an explicit shape specification and shape specification expression is a constant expression. If <i>N</i> is omitted, the compiler determines the amount of padding for each target array. The padding creates a gap in the array. |

| -Karraypad_expr=N<br>(1≦N≦2,147,483,647)    | Pads <i>N</i> elements of an array whose first dimension is an explicit shape specification, regardless of whether its shape specification expression is a constant expression.                                                                                                               |

## Use example (source code before improvement)

\$ frtpx -Kfast,parallel sample.f90 -Karraypad\_expr=1

Notes

- •Options must be specified for all source code that uses the target arrays.

- •The effects of padding vary depending on the program.

- •Incorrect use may result in different computational results.

- •The -Karraypad\_const [=N] option and -Karraypad\_expr=N option cannot be specified at the same time.

# Padding That Increases the Number of Array Elements in the Second Dimension

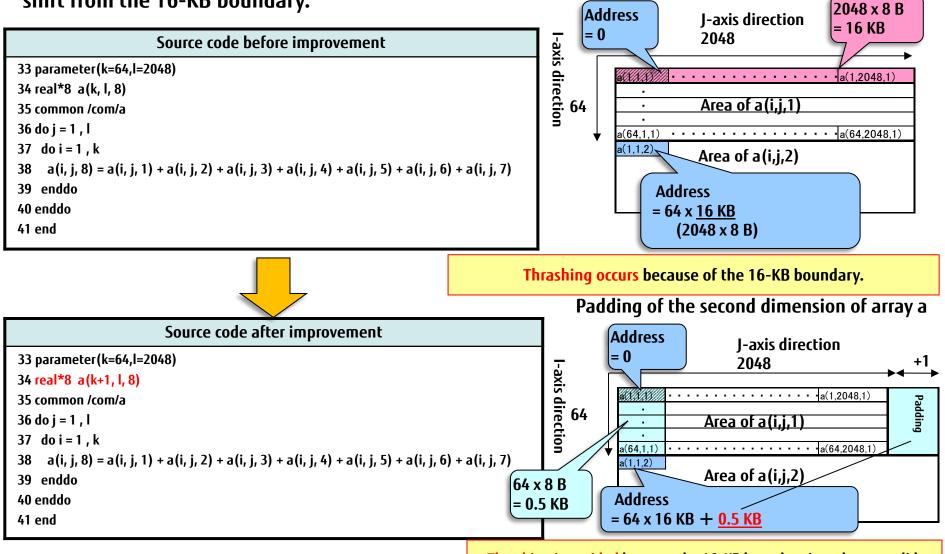

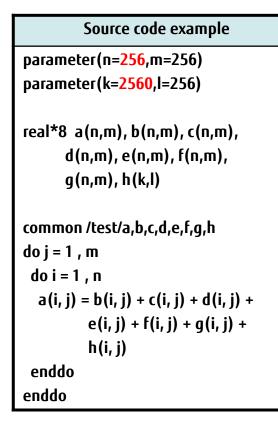

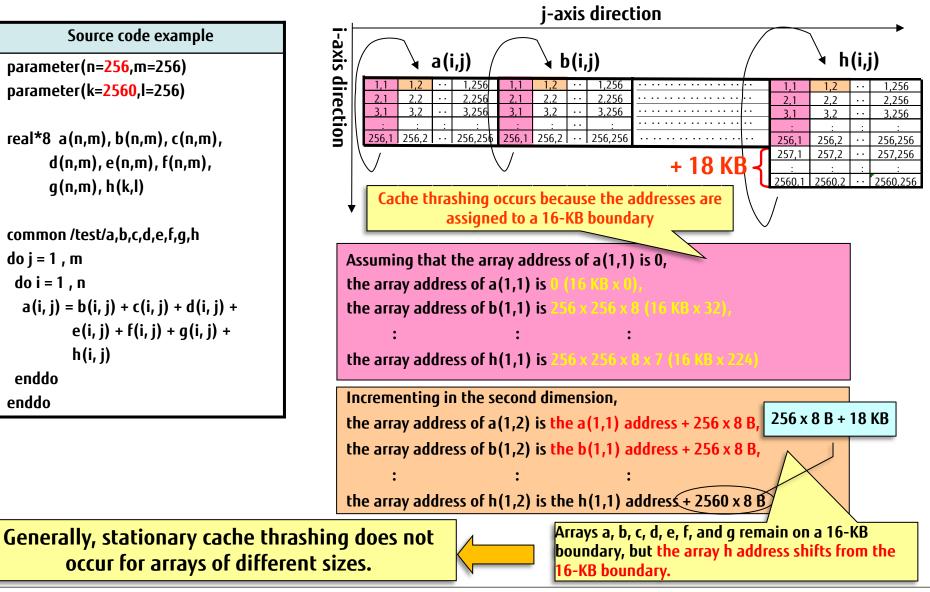

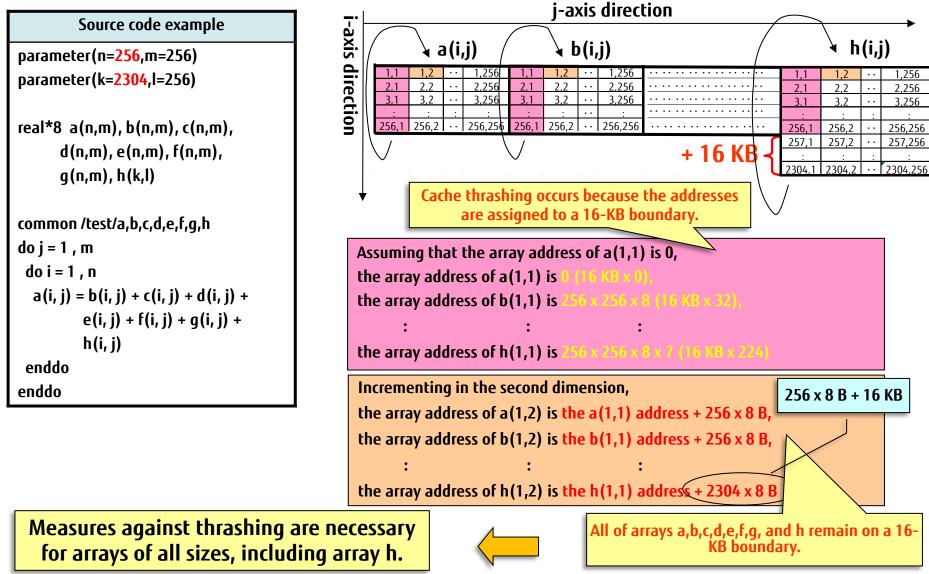

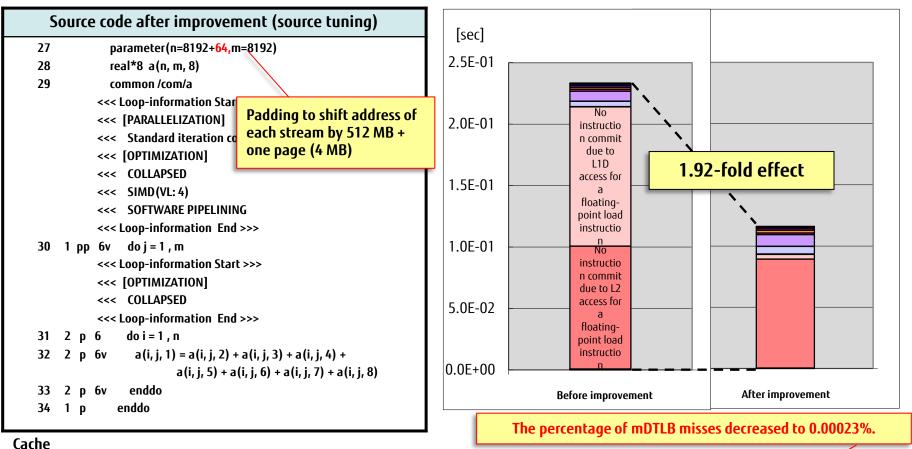

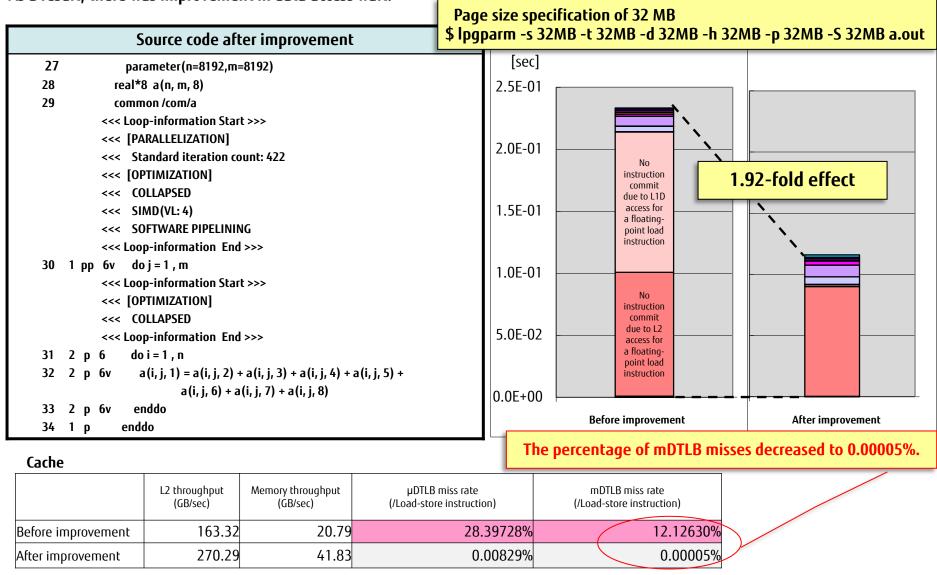

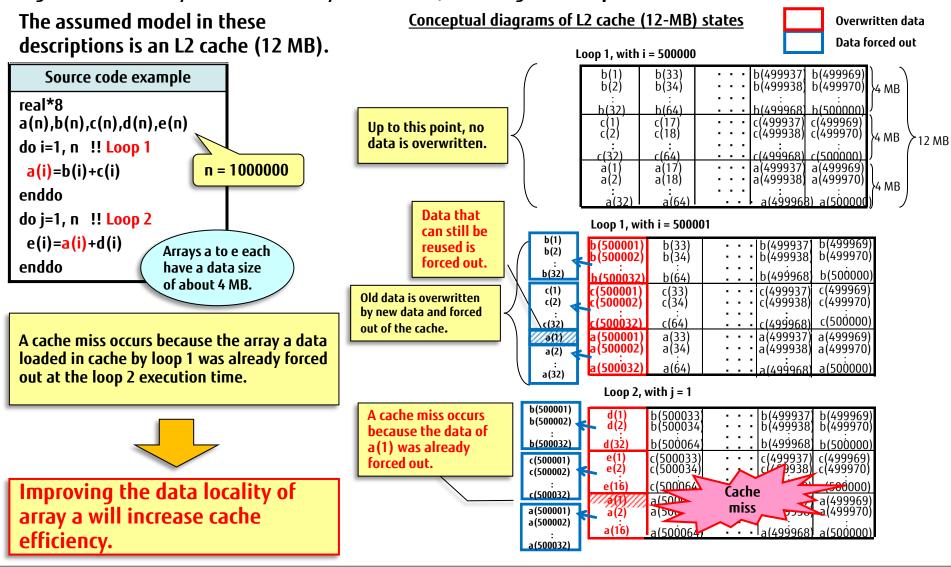

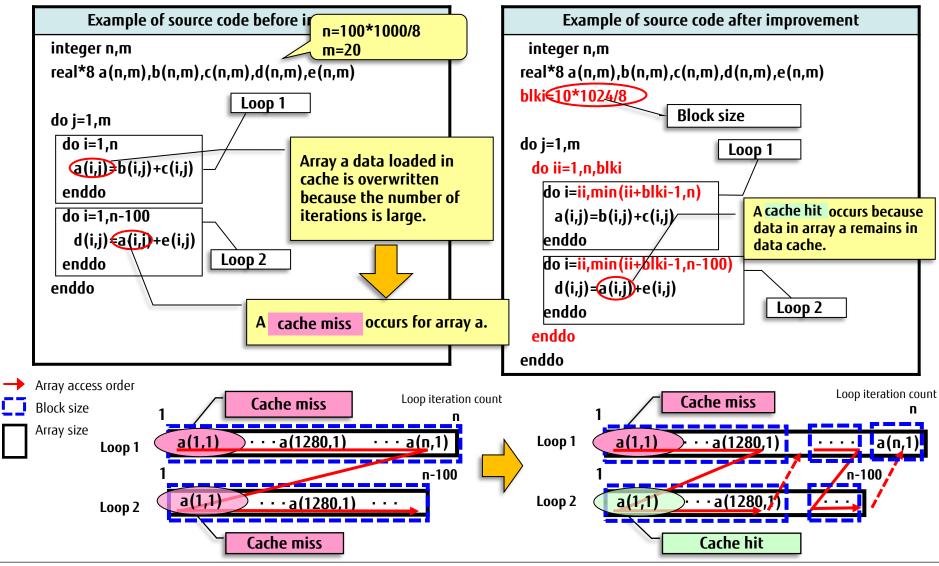

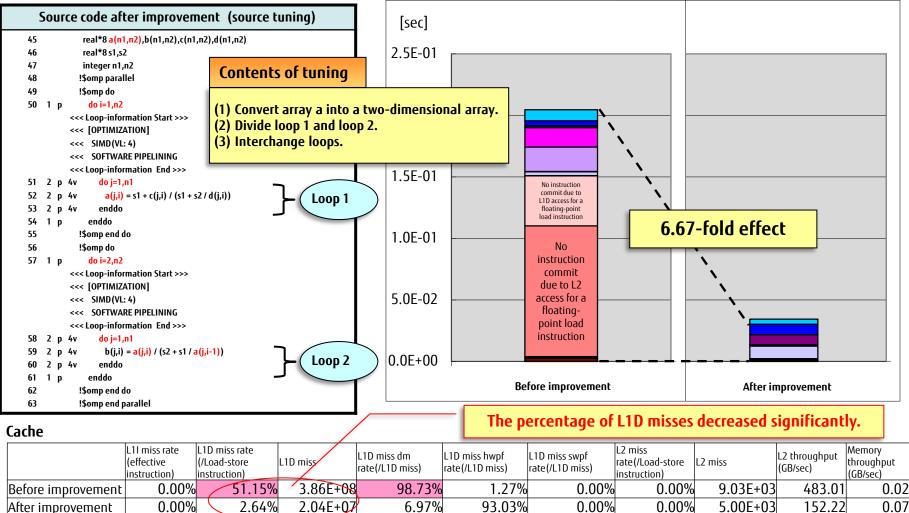

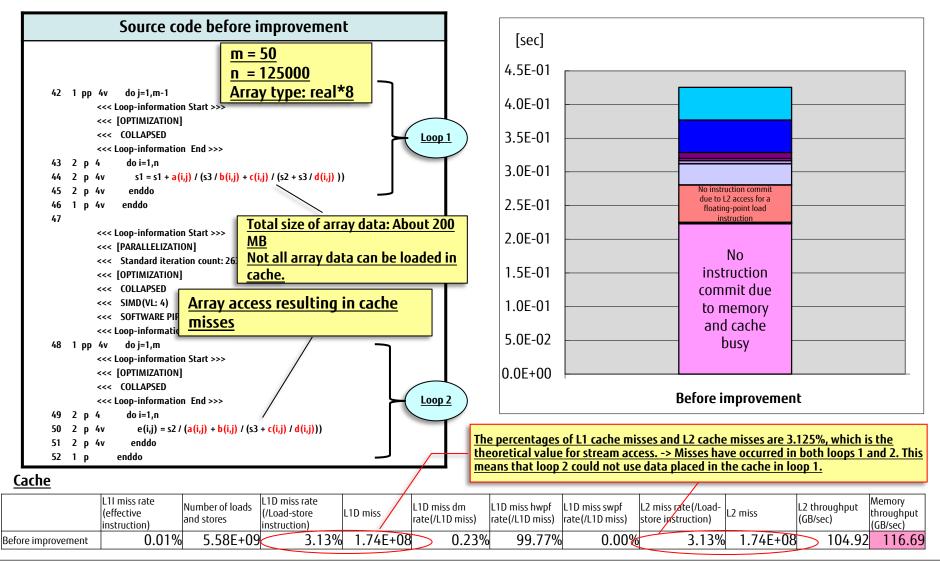

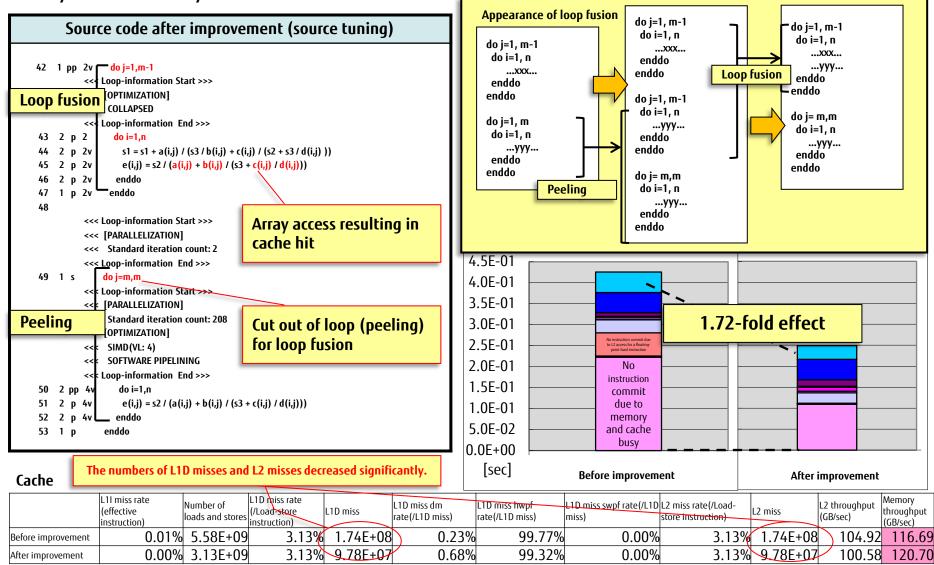

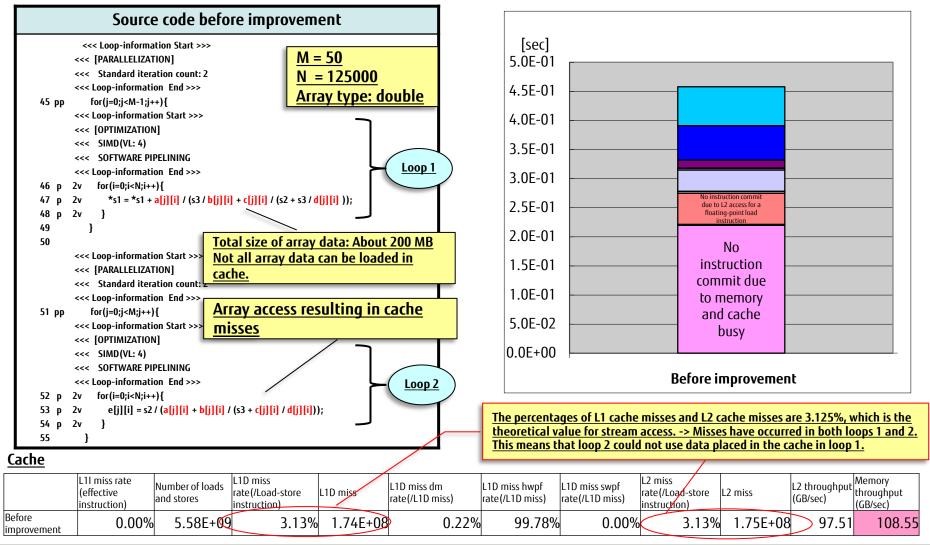

- Case of No Improvement from Padding That Increases the Number of Array Elements in the First Dimension